Other Parts Discussed in Thread: ALP

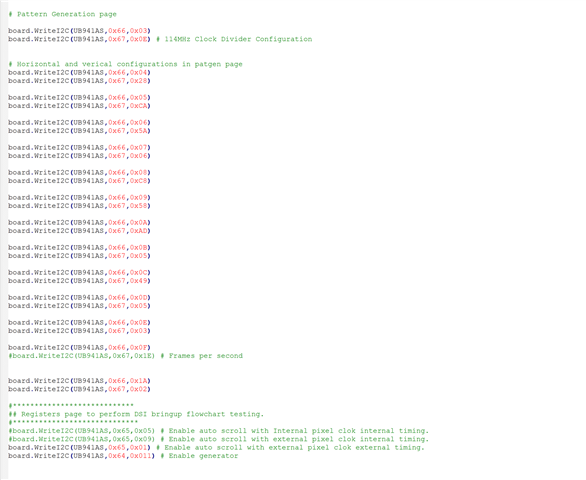

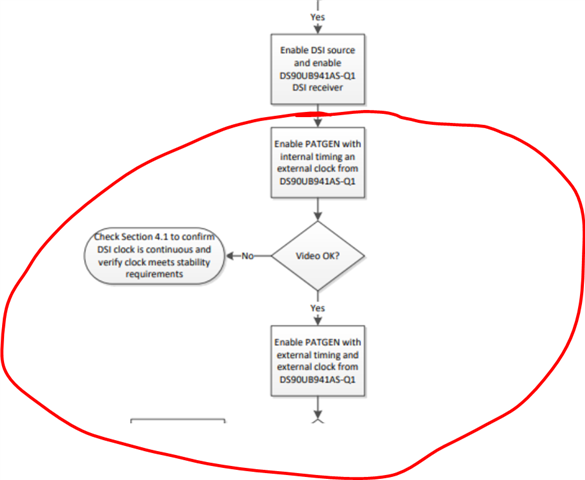

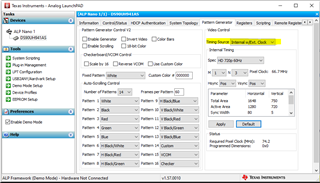

We are following the DSI bring-up guide for the DSI bring-up. For some boards, we are getting some CRC errors when using the pattern generator configured with external timing. The CRC error rate differs between board to board, ranging from ~6 errors every few seconds, to ~6 errors every 30 minutes. Included are some register dumps for reference. Are there any registers or configurations in particular that we can tune, to improve the CRC error rate?

Note: we are not getting any CRC errors at some boards.

Serializer - DS90UB941,

Deserializer - DS90UB948

0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef 00: 18 00 00 92 00 00 68 00 00 01 6e 00 47 35 00 00 ?..?..h..?n.G5.. 10: 00 00 00 bb 00 00 fe 9e 7f 7f 01 00 02 00 01 00 ...?..?????.?.?. 20: 0b 00 25 00 00 00 00 00 01 20 20 a0 00 00 a5 5a ?.%.....? ?..?Z 30: 00 09 00 05 0c 00 00 00 00 00 00 00 00 00 81 02 .?.??.........?? 40: 05 3b 03 00 00 00 00 00 00 00 00 00 00 00 00 8c ?;?............? 50: 16 00 00 00 02 00 00 02 00 00 c9 80 07 06 44 72 ?...?..?..????Dr 60: 22 02 00 00 11 01 00 00 00 06 00 00 00 00 20 00 "?..??...?.... . 70: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 7c 00 ..............|. 80: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ 90: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ a0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ b0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ c0: 00 00 82 00 68 08 41 00 40 00 00 00 00 02 ff 00 ..?.h?A.@....??. d0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ e0: 00 00 82 00 68 08 41 00 00 00 00 00 00 02 00 00 ..?.h?A......?.. f0: 5f 55 42 39 34 31 00 00 00 00 00 00 00 00 00 00 _UB941.......... DSI Register Display - ALP Nano 1 - DS90UH941AS, Connector 1 Register Data Name 0x0001 0x00 DPHY_TINIT_TIMING 0x0002 0x00 DPHY_TERM_TIMING 0x0003 0x1D DPHY_CLK_SETTLE_TIMING 0x0004 0x14 DPHY_HS_SETTLE_TIMING 0x0005 0x22 DPHY_SKIP_TIMING 0x0006 0x00 DPHY_LP_POLARITY 0x0007 0x00 DPHY_BYPASS 0x0008 0x00 HSRX_TO_CNT 0x000F 0x1F DPHY_STATUS 0x0010 0x00 DPHY_DLANE0_ERR 0x0011 0x00 DPHY_DLANE1_ERR 0x0012 0x00 DPHY_DLANE2_ERR 0x0013 0x00 DPHY_DLANE3_ERR 0x0014 0x00 DPHY_ERR_CLK_LANE 0x0015 0x00 DPHY_SYNC_STS 0x0020 0x7F DSI_CONFIG_0 0x0021 0x00 DSI_CONFIG_1 0x0022 0xFF DSI_ERR_CFG_0 0x0023 0x7F DSI_ERR_CFG_1 0x0028 0x05 DSI_STATUS 0x0029 0xFF DSI_ERR_COUNT 0x002A 0x3E DSI_VC_DTYPE 0x002B 0x80 DSI_ERR_RPT_0 0x002C 0x00 DSI_ERR_RPT_1 0x002D 0x02 DSI_ERR_RPT_2 0x0030 0x00 DSI_HSW_CFG_HI 0x0031 0x20 DSI_HSW_CFG_LO 0x0032 0x00 DSI_VSW_CFG_HI 0x0033 0x04 DSI_VSW_CFG_LO 0x0034 0x00 DSI_SYNC_DLY_CFG_HI 0x0035 0x20 DSI_SYNC_DLY_CFG_LO 0x0036 0x00 DSI_EN_HSRX 0x0037 0x00 DSI_EN_LPRX 0x0038 0x00 DSI_EN_RXTERM 0x003A 0x02 DSI_PCLK_DIV_M 0x003B 0x03 DSI_PCLK_DIV_N