Hi experts,

We are using ub927 and ub940 for application as below:

Issue:

ub940 lock status ok,but soc mipi receiver can not sync to valid mipi clock.

Test has been done:

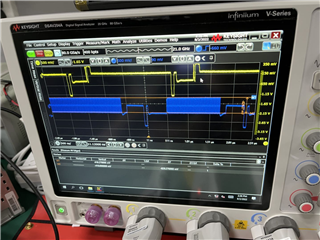

1.We monitored the mipi clock with the oscilloscope and the result is as below:

By comparing with the correct board, we discovered that the voltage amplitude of mipi clock of the failed chip is 829 mv,which is larger than the max value in mipi dphy specification(500 mv). The part number of the failed chip is dsub940n.

2. In our software start up sequence, first we set ub940 test pattern with internal clock and then close test pattern and switch to normal mode. We close the test pattern and let the chip work directly in normal mode and the black screen can not be displayed.

Could you please explain in details that why closing test pattern can avoid black screen issue?

3. We did fota update of the whole system and when the system restarts from fota update, the i2c communication between the host machine and ub940 can not work. When we apply the oscilloprobe to measure the i2c waveform, the communication recovers. Could you please explain why?

Thanks in advance!