Part Number: DS90UH947-Q1

Other Parts Discussed in Thread: ALP

Hi Team,

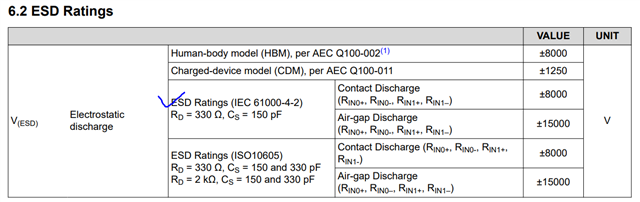

As title, we failed the ESD test when test item was air 4kV and we used 947 internal pattern generation to bring up the panel. The failed behavior was that black screen when did the ESD test, but auto recovery.

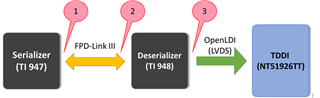

And we didn't see the issue when using 948 internal pattern generation. So we think the root cause may be link of SerDes.

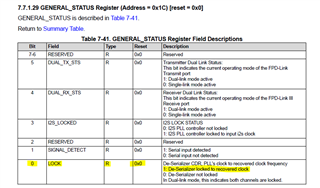

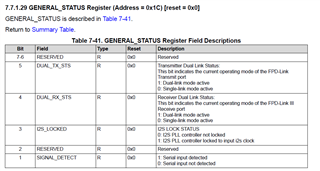

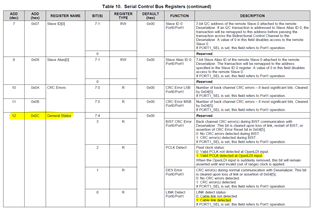

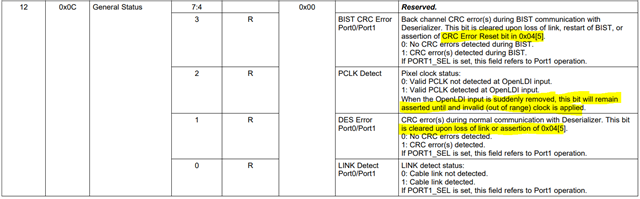

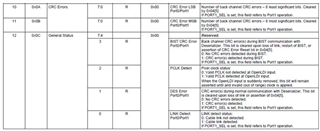

We tried to read 947 0x0A, 0x0B, 0x0C before/after ESD test, but we didn't see the abnormal data.

Do you have any recommended register that we can read to indicate the root cause?

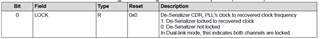

Below is our operating diagram. And all we know is that the TDDI register indicated the wrong CLK.

Regards,

Roy