Hi experts!

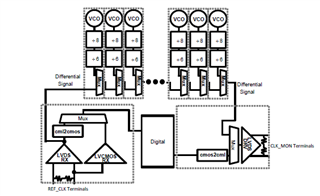

I’m exploring daisy chaining the clock for several DS125DF1610 (16-channel re-timers) together. My understanding from the data sheet is that the “output” clock pins, CLK_MON_P/N, are LVDS (compatible) outputs. It is not clear from the datasheet if the input clock pins, REF_CLK_P/N, include an on-chip termination.

- Do the input clock pins include an on-chip termination for LVDS inputs?

- If not, what is the recommended termination style given that the inputs must be AC coupled in differential mode?

- Worth asking, do the differential clock inputs HAVE to be AC coupled?

Thanks for your help!

Best regards,

Jim B