Part Number: DP83826E

Hello,

I have implemented the DP83826 on a test hardware to gain experience with it for my company. I am encountering problems with the link setup. I have tried using the troubleshoot file to find the error, but to no avail.

The DP83826 is controlled on the hardware with a Max1000 FPGA board. Via this comes the 25 Mhz clock, the reset signal and the supply voltage. The schematic of the board is attached.

Now I try to communicate with my PC via a USB-Ethernet interface. Here I check the LED 0 and the LED 1 to be able to make a statement about the link. Thereby I observe something quite unusual:

At the beginning the LED 1 goes low, which means that there is a 100 Mbit communication. But this is interrupted several times and LED 1 toggles irregularly. After a few seconds at most, LED 1 is permanently high. LED 0 continues to toggle until it goes low, indicating that a link is being established. However, a link with 10 Mbit and not 100 Mbit is created.

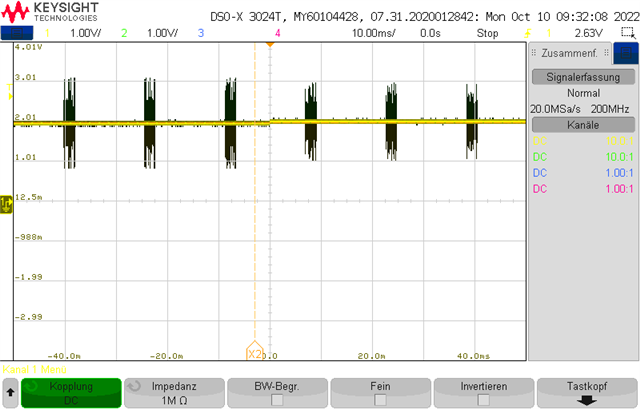

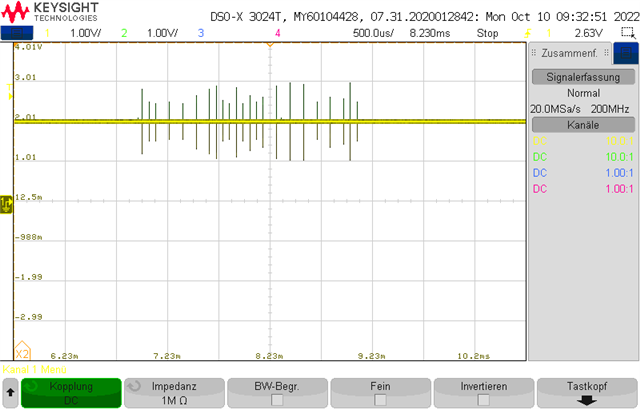

After the auto-negotiation procedure a 100 Mbit link should be created. I attach the measured data pulses in the appendix. On both TX and RX I measure the correct Fast Link pulses.

I checked the clock, the supply voltage on both pins, the reset signal and also the PWRDN input. I started reading out the registers and carried the results into an Excel. Here I did not find any error. Are there any other typical sources of error in the link setup?

Thanks in advance for the help

Best Regards

Florian Haug