Hello TI Team,

We are using DP83822 PHY in a backplane application.

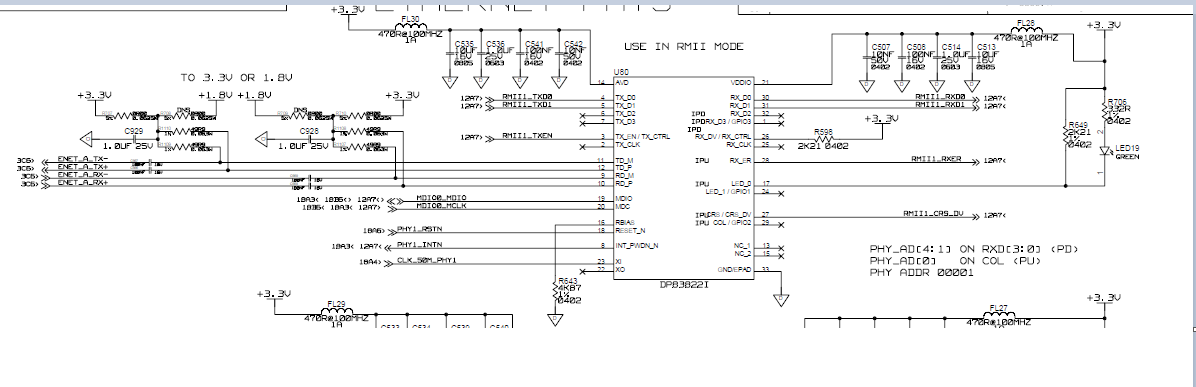

The PHY is configured in RMII Slave (50MHz clock) The device is configured in 100bT mode, Class A, and the TX and RX lines are capacitively coupled and biased as per the Fig 9-3 in the datasheet with 1.0uF and 0.1uF bulk capacitors on the 3.3V rail as shown in fig 9-2.

The other end is connected through a backplane to a Marvell Phy with similar biasing.

DP83822I has auto-negotiation enabled and Marvel Phy is configured in fixed 100Mbps full duplex mode.

Our customer reported FCS errors on their pack. Could you please let us know if there is anything we can try on the hardware or software side to fix this issue?

Schematic below:

Your help is greatly appreciated!

Thanks,

Swapna