Part Number: DS100DF410EVK

Other Parts Discussed in Thread: DS100DF410

Hello, This is my first post.

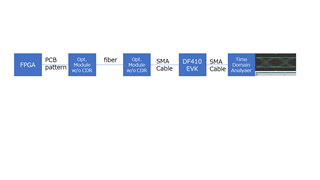

We are considering a 10GbE re-timer using the DS100DF410EVK.

What settings can be used to reduce jitter?

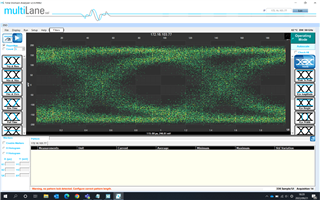

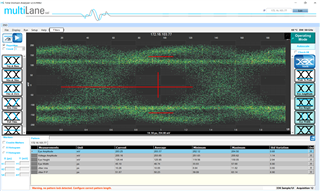

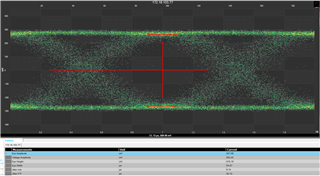

The above is input eye wave.

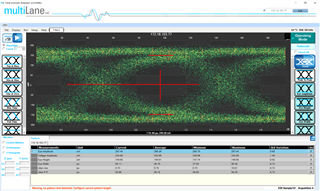

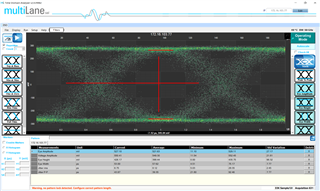

The above is output eye wave through DS100DF410EVK.

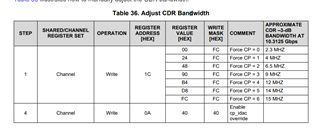

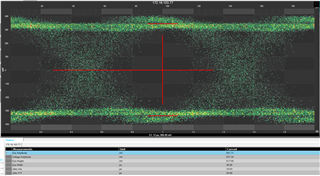

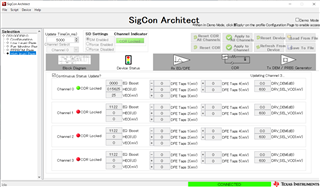

The current SigCon status is below.

Thanks.