Part Number: DS100BR111A

Other Parts Discussed in Thread: DS100BR111

Hi Team,

For DS100BR111A,

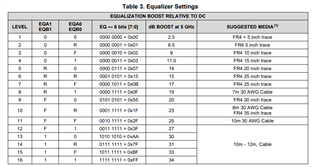

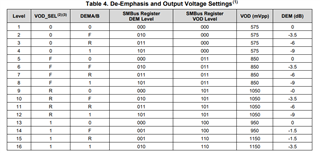

In pin mode, must the pull-up and pull-down states of EQA1 and EQB1 be the same?

In addition, when debugging EQ and DEM, what is the recommended direction? Which one to call first?

Do the answers to the above two questions also apply to DS100BR111? Thanks.

Regards, Charlie