Hi, TI support team

The following inquiries have been received from customers.

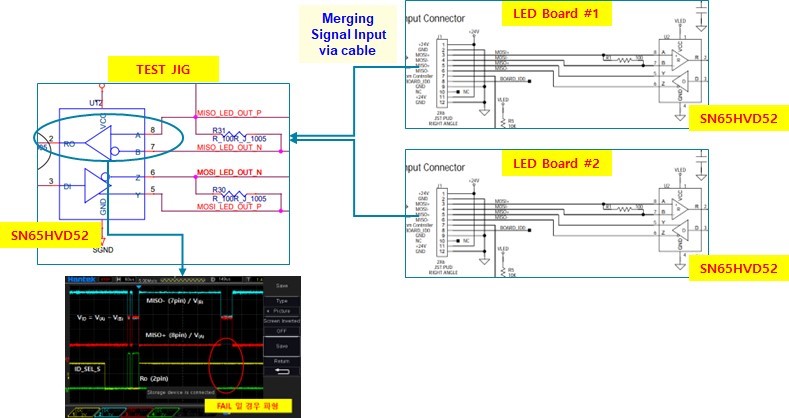

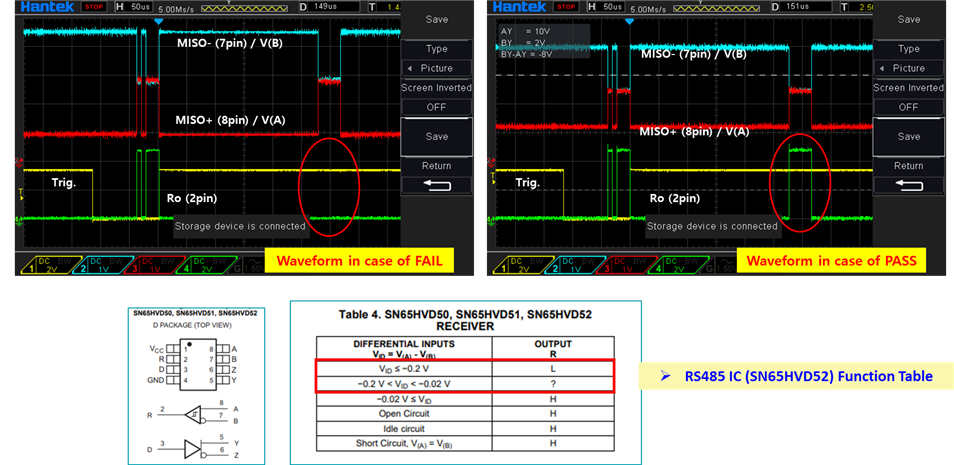

This is an inquiry about abnormal operation of SN65HVD52DR.

1. The signal of R output (2pin) is output differently according to the difference of 7,8 pin input signal of SN65HVD52DR (RS-485 IC). What is the cause?

2. In the function table of the data sheet, -0.2V<VID<-0.02V is marked as OUTPUT (R)->? What does "?" mean?

3. Does the differential input signal need to overlap for stable operation?

See picture below.

Thanks.

Regards,

MJ