Hi TI members,

We are having a survey on using TI PCIe MUX(SN75LVPE5421) in our design.

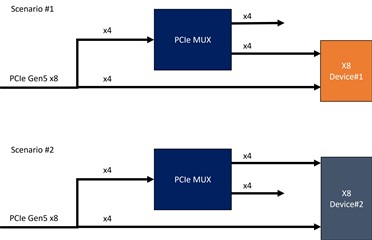

But in our application, we use one x8 PCIe Gen5 port coming from CPU and only x4 of them route into PCIe MUX.

The other x4 doesn't go through PCIe MUX.

But in the end device, we will still combine the two x4 into one x8 device.

Which means in x8 signals there will be x4 having a delay in PCIe MUX, the other x4 won't.

I've checked the spec, there is 90~130 ps latency in MUX.

Does TI used to have a study on this? And if it is feasible?

Also, we are thinking if need to route with different length on each x4 for timing compensation.

Would need TI's suggestion on this.

Appreciate!

Best Ragards,

Clement Lee