Hi,

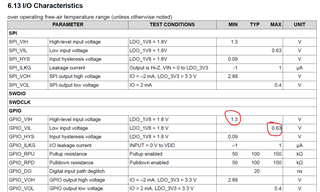

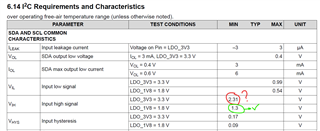

We have an ARM processor based application which needs to control TPS65987DDJ through I2C lines. But the processor's IOs support only 1.8V. It was not clear to me in the datasheet whether TPS65987DDJ's I2C lines are directly compatible with 1.8V logic levels. So here are my questions:

1. Can I connect our host processor's I2C lines directly without any level shifter to TPS65987DDJ's I2C lines?

2. Our host processor's I2C bus acts as a master (produces clock). The host processor should be able to send some commands like "Switch to Source" or "Switch to Sink" mode like we have it in configuration tool. Also in the future we may need to upgrade external flash content through TPS65987DDJ. In this case it is confusing which I2C bus of the TPS65987DDJ should be used. It has 3 buses, called I2C1, I2C2 and I2C3. I2C3 is always master, obviously that is not the one. I2C2 is indicated as always slave, as I understand we can use it directly as evaluation board that we have did. but I wonder if there is any slave functionality that we can do through I2C1 which is by default slave (but can be configured as master, which we don't want that) but can not do with I2C2?

Thanks.