Part Number: SN65DP159

Other Parts Discussed in Thread: SN75DP159

Hi,

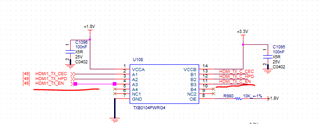

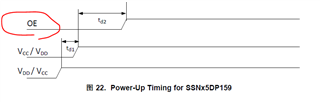

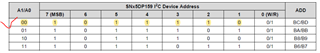

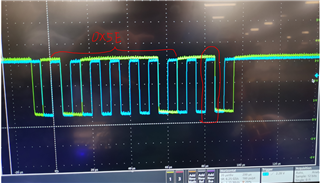

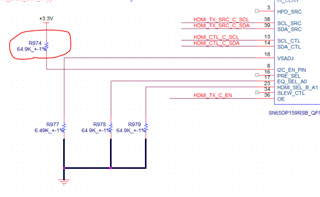

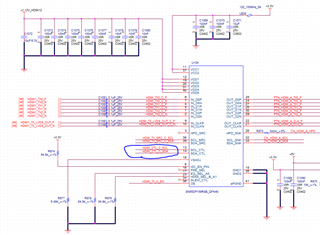

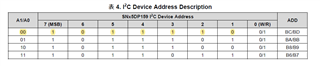

During accessing control IIC interface of SN65DP159, I found no any response from this IIC interface. So, I used oscilloscope to test SCL and SDA , and ninth data is not low that means I can't receive ACK signal from SN65DP159 . I interpret the IIC device address from the test curve on the oscilloscope, and it match first address in the address table. Then I test VDD and VCC, and they are all right. The schematic is shown below, it almost copy the official design.

Could you please help me check this issue ? Any information will be appreciated.

Thanks in advance!!!

Best regards!!!

Jason