Hello support team,

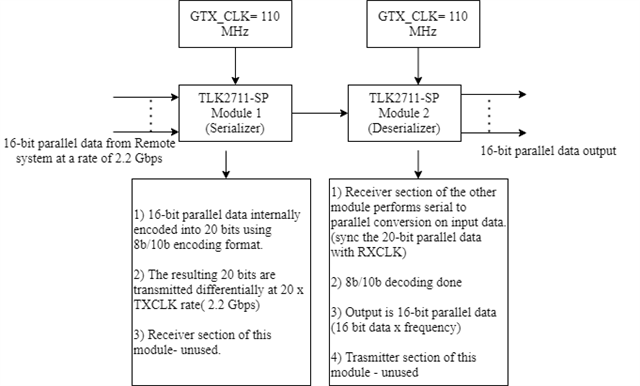

Please find attached reference block diagram for the TLK2711-SP. We are thinking to use 2 different TLK2711-SP out of one module will be used as a serializer and another module as a deserializer. Is the below block diagram is correct to receive accurate data at the output of module-2. What are the factors we need to take care so that we don't face any problem like bit misalignment, missing data? could you please provide some guidance.

Also, do we need to synchronize the both GTX CLK for this kind of multiple module of TLK2711-SP?

Awaited your feedback and response.