Hello, I have some questions, please help

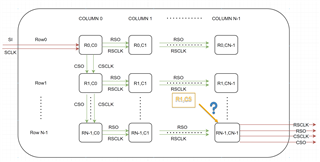

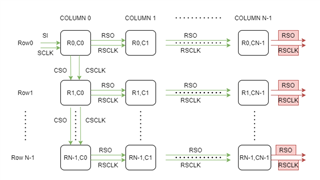

1.According to SPEC requirements, my understanding of the connection is shown in the figure. Please help to confirm whether RSO and CSO are connected correctly and appear in appropriate rows or columns.

2.If i want to read the config register value of the specified DS90CP04 device, shoule connect all the RSO and RSCLK of the last device in each row to the Host? and how about CSO and CSCLK of the last device in each row (In red above)

3.According to your observation, is it necessary to draw out the serial interface for read ,because we have so much rows. The host pin resource is limited.

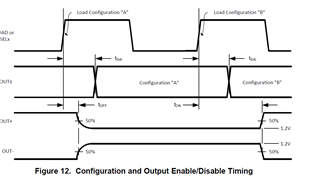

4.I don't quite understand the picture below, please help to explain:

4.1Are ConfigA and ConfigB two configurations in the same device? Doesn't a device theoretically have only one configuration in Load register? My understanding is: for example, in the NxN matrix, all devices are successively written to the load register. So A and B are the same config, right? The second load rising edge is purely to open OUT, but the second contents of the load register are the same, right?

4.2LOAD pin in L->H->L->H ,In the process of H state, except timing between OUT and LOAD is considered(tsw,toff,ton),is there a requirement for the maximum duration of the LOAD signal's high level? And is there a maximum and minimum time requirement for a low level between two high levels? Because we want to use a low speed IO to control the signal, the LOAD frequency will not be too high.

4.3 After programming is completed, Can LOAD be pulled up at any time to transfer load register's content ?Any time?

5.In the crosspoint matrix, if the former stage DS90CP04 is connected to the next stage DS90CP04, is it necessary to add 100R end-resistor for LVDS at next stage DS90CP04?