Hi,TI

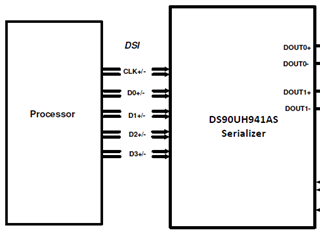

In bring up,FPD-LINK has the following problems.Please refer to the simple system block.

/resized-image/__size/320x240/__key/communityserver-discussions-components-files/138/3146.block.PNG

1. At initial power-up, the 948's lock signal was unstable. When the PDB is high, the LOCK is stable high after 1s.

2. Some control signals are configured through the local GPIOs of the 948, but occasional failures occur.

Seen by a logic analyzer,when LOCK is low, the SOC is configuring the registers on the 948 side through the 941.

Does this cause the above problem?

For this case,please help answer the following questions

1. What is the reason for the LOCK instability at initial power-up

2. Will the EVM board LOCK also appear unstable?

3. When LOCK is low, can I initially configure the 948?Can I I2C configure a 948-side slave device?

4. Refer to Table 2. Output State Table, Reg 0x02 [7] and Reg 0x02 [4] need to be configured to 1 when 948 is initialized?

5. What value is usually configured for Reg 0x02 initialization, and is bit5 only used during BIST?

Thanks