Part Number: DS90UB954-Q1

Other Parts Discussed in Thread: DS90UB953-Q1

hello team:

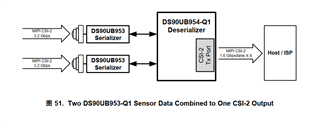

ds90ub954 is connected to two ds90ub953a,each ds90ub953a is connected to one image sensor(imx307).How to config the registers of ds90ub954 and ds90ub953 ?

The following is our register settings, now the sensor cannot work properly. reported cci error . pls help to check it, thanks !

// 954

{0x01,0x04,0x00},

{0x1F,0x00,0x0}

{0x11,0x21,0x0}

{0x32,0x01,0x00},

{0x4c,0x01,0x00},

{0x58,0x5e,0x00},

{0x5c,0x30,0x00},

{0x5d,0x34,0x00},

{0x65,0x34,0x00},

{0x6d,0x7C,0x00},

{0x7C,0x00,0x00},

{0xB9,0x3F,0x00},

{0x72,0xE4,0x00}

{0x32,0x01,0x00},

{0x4c,0x12,0x00},

{0x58,0x5e,0x00},

{0x5c,0x30,0x00},

{0x5d,0x34,0x00},

{0x65,0x34,0x00},

{0x6d,0x7C,0x00},

{0x7C,0x00,0x00},

{0xB9,0x3F,0x00},

{0x72,0xE1,0x00}

{0x32,0x01,0x00},

{0x4c,0x01,0x00},

{0x58,0x00,0x00},

{0x32,0x01,0x00},

{0x4c,0x12,0x00},

{0x58,0x00,0x00},

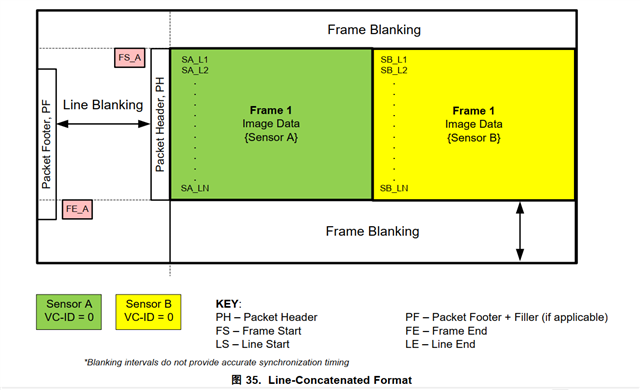

// stream

{0x32,0x01,0x0},

{0x33,0x23,0x0},

{0x20,0x00,0x0},

{0x21,0x81,0x0}

// port 2

{0x20,0xe0,0x0},

{0x32,0x01,0x0},

{0x33,0x00,0x0}

//port 1

{0x20,0xd0,0x0},

{0x32,0x01,0x0},

{0x33,0x00,0x0}

// 953

{0x01,0x01,0x0}

{0x02,0x73,0x0}

{0x05,0x0b,0x0},

{0x33,0x00,0x0},

{0x02,0x73,0x0}

{0x0d,0xf0,0x0},

{0x0e,0x0f,0x0}