Part Number: SN65DPHY440SS

Hi,

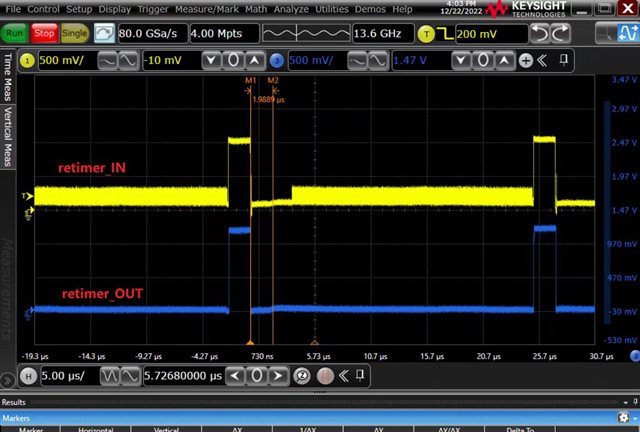

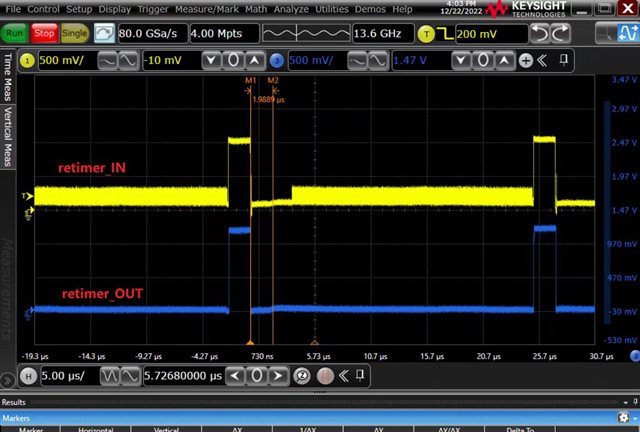

There is data input, but no HS output data. What's the reason?

Thanks!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: SN65DPHY440SS

Hi,

There is data input, but no HS output data. What's the reason?

Thanks!

Hi,

Are you seeing this issue on lane 0?

DPHY440’s LP TX is expecting to connect to an unterminated LP RX. With Lane 0 path (DA0P/N and DB0P/N) supporting bi-directional LP signaling, it is very important that DB0P/N LP TX is connected to an unterminated LP RX. If DB0P/N LP TX is connected to a HS RX, then LP signaling will not be able to reach the LP11 levels and which will cause the DPHY440 to not enable HS data path on Lane0.

Try following for enabling lane0 HS path:

Enable HS path for Lane 0 only:

Write Register 0x50 with 8’h01 //Override enable for HS TX path

Write Register 0x51 with 8’h01 //HS TX path enabled.

Write Register 0x61 with 8’h00 // Disable LP path.

Write Register 0x70 with 8’h01 //Override enable for HS RX path

Write Register 0x71 with 8’h01 // HS RX path enabled.

Bit 0 is lane 0

Thanks

David