Other Parts Discussed in Thread: LSF0101, 2N7001T, TXU0101, SN74LVC1G07

Hello E2E Experts,

Good day.

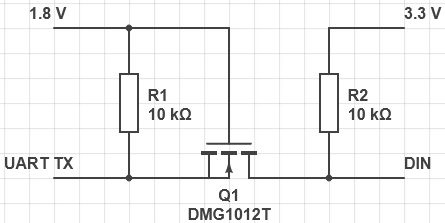

Please share the internal structure of the TCA5405 to understand what should be the value of the pull-down resistor in the attached push-pull level conversion logic. The datasheet is very stingy with details.

Thank you in advance.

Regards,

CSC