Part Number: DS250DF230

Hi, TEAM.

Our customer has asked us about a DS250DF230 with unstable CDR locks.

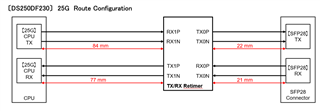

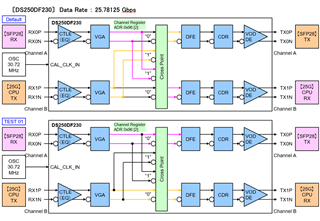

The block diagram in the upper part of the image (Default) is the configuration used in the operation.

The Cross Point of DS250DF230 is enabled and routed below.

CPU(LX2160A) --> DS250DF230 --> SFP28

SFP28 --> DS250DF230 --> CPU(LX2160A)

The block diagram in the bottom row (TEST 01) is the configuration looped back for verification.

The Cross Point of DS250DF230 is not switched, so the route is as follows.

CPU(LX2160A) --> DS250DF230 --> CPU(LX2160A)

SFP28 --> DS250DF230 --> SFP28

In the two configurations, the CDR lock of the input signal (RX1) from CPU(LX2160A) is not stable, so the configuration in TEST 01 in the bottom row is verified.

Using the GUI tool of "SigCon Architect

Data rate: 25.78125 Gbps

Calibration Clock Pin (CAL_CLK_IN) of DS250DF230 is 30.72 MHz.

Signal Detected of input signal (RX1) from CPU (LX2160A) is OK.

Input signal (RX1) from CPU (LX2160A) is CDR Locked/Unlocked.

25G_Retimer_setup_01.cfg25G_Retimer_setup_01.xlsx

The attached "25G_Retimer_setup_01.cfg" is the data saved from "SigCon Architect".

data saved from "SigCon Architect".

Setup and start of operation is only as follows.

1 "Reset Device

2 "Apply to All Channels

3 Reset CDR All Channels

Sheet "test_01" in "25G_Retimer_setup_01.xlsx" is each screen on "SigCon Architect".

test_01_01.bmp CDR Unlocked(Channel 1 blue box)

test_01_01a.bmp CDR Locked(Channel 1 blue frame)

The CDR lock is not stable.

I would like to get advice on where to check and what settings to make in order to stabilize the CDR lock.

Best Regards,