Part Number: DS90UB948-Q1

Hi Expert,

We have questions below. Please kindly help check.

Restart AEQ, the EQ(0x3B) status is zero. after running for some time, EQ status suddenly changes to 0x20, then LVDS signal abnormal is detected.

948 LVDS output is connected to ROHM IC, below errors are detected from ROHM side.

- H_TOTAL_MAX_FAIL_H

- System fail (LVDS input DE/Clock fail) State, because clock is OK, maybe DE fail

Even if EQ status changes to 0, LVDS signal abnormal always existed, not recoverable.

948 Lock pin is high level, LVDS clock should be OK.

Could you help check if the timing of restarting AEQ is right? When issue occurred, 948 output LVDS signal always abnormal, is it possible 948 work abnormally? Because of no such issue without restart AEQ.

Below is restart AEQ

- Restart AEQ by modifying the 948 register:

0x35=40h

0x35=00h

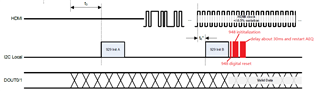

- Restart AEQ timing

Thanks!

Ethan Wen