Other Parts Discussed in Thread: DP83TC811, DP83TC812S-Q1

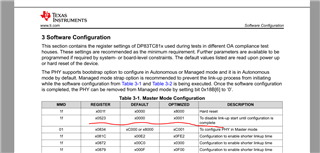

In the SNLS579A document for DP83TC811, register 0x485 bit 12 is link control bit, but in the SNLA293

for both master and slave configuration register 0x475 bit 4 is used for link control.

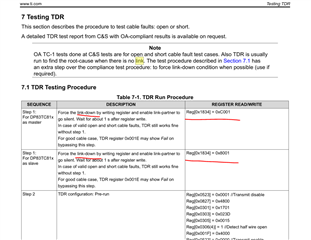

1) When the the device is initialized, is bit 12 in register 0x485 enough for setting the link control?

2) For DP83TC812 only bit in SNLA389A Open Alliance document (register x0523, bit 0) is mentioned, is

for handling link control this bit enough or is there another bit, like bit 12 register 0x485 for DP83TC811,

which is not documented in SNLS document?

3) Is the link control handling of DP83TC812 similar to DP83TC811 or is disabling/ enableingt of he link control for DP83TC812 not supported in hw