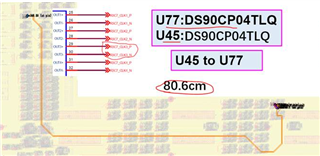

Many TI DS90CP04 clock drivers are used in our project, and the longest topology is as follows: U77 transmitter and U45 receiver both use DS90CP04 chip:

The longest CLK length is 80.6cm, and the maximum clock frequency that needs to be supported is 700MHz For such link topology, we have the following problems and need your strong support. Thank you

1.What is the maximum link length supported by DS90CP04 chip at 700MHz clock frequency? Is there any test data from TI?(Our design link is too long. How do we identify our design risk?)

2.What methods do we have to evaluate the reliability of DS90CP04 chip link topology?

3.n the IBIS model of DS90CP04 chip on TI's official website, the reflection after connecting the driver end is particularly large during the simulation. What should we pay attention to when using DS90CP04 chip to run CLK SI simulation to evaluate the link length? (Simulation frequency 700MHz)

4.Is the input/output of DS90CP04 internally physically switched or redriven?