こんにちは

DP83867IRについて下記の点を教えてください。

1.弊社基板の回路構成

(1)DP83867IRの電源構成は、Two-Supply Configurationで構成してます。

また、VDD*端子には下記の電圧を供給しています。

・VDDA1P0:1.0V

・VDDA2P5:2.5V

・VDDIO : 3.3V

・VDDA1P8:オープン

(2)XI端子については、水晶発振器を使用し供給しています。

また、水晶発振器は、1.8Vの電源で構成しています。

また、XO端子は「OPEN」です。

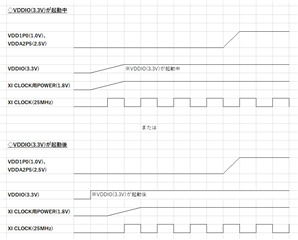

(3)電源投入シーケンスは下記になります。

・水晶発振器に1.8V電圧を供給

・VDDIO端子に3.3V電圧を供給

・VDDA1P0端子に1.0V、VDDA2P5に2.5V電圧を供給

【質問1】

・電源投入シーケンスについて確認させてください。

下図では、「XI CLOCK 投入」 → 「VDD*電源投入」の順序になっているが、

VDDIO(3.3V)、VDDA1P0(1.0V)、VDDA2P5(2.5V)が入力される前に、

XI CLOCK(1.8V)を入力しても問題はありませんか?。

デバイスに電源が入力される前(無通電時)にクロックが入力される場合、デバイスに損傷を与えたりしますか?

【質問2】

・DP83867IRですが、XI端子ですが、デバイスに電源が投入される前(無通電時)に

水晶発振器より、XI CLOCKが入力されても問題はありますか?

XI端子はラッチアップの耐性がある端子ですか?

【質問3】

VDDIO電源とクロックの投入順序はありますか?

VIOIO電源(3.3V)供給後にクロックを投入する必要がありますか?

「VDDIO(3.3V)を投入」→「水晶発振器(1.8V)を投入」→「VDDA1P0(1.0V)、VDDA2P5(2.5V)を投入」

の順にする必要がありますか?