Other Parts Discussed in Thread: RM46L852, TCAN4550

Dear

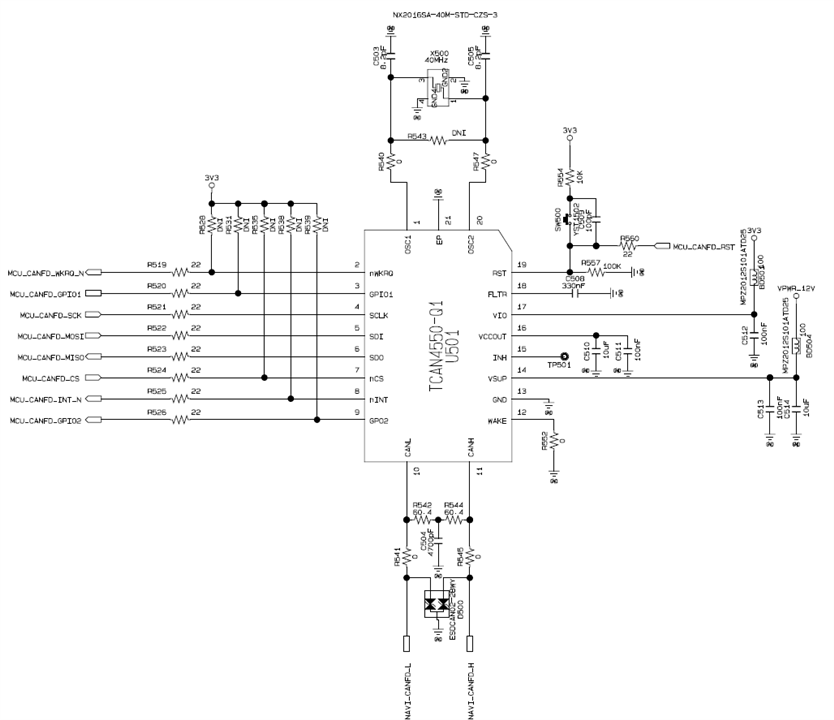

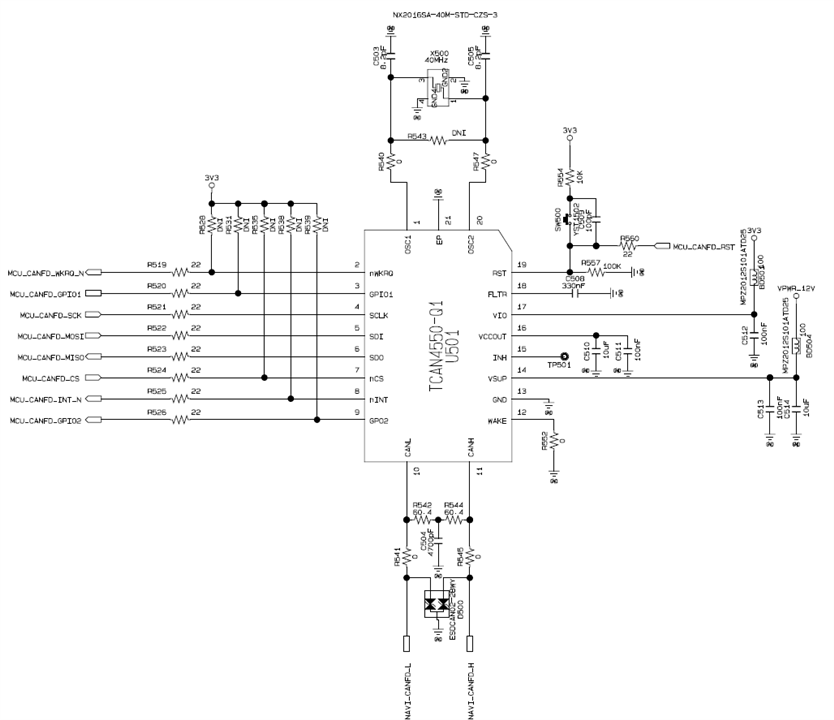

Request for TCAN4550 circuit diagram review.

RM46L852

TCAN4550

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Dear

Request for TCAN4550 circuit diagram review.

RM46L852

TCAN4550

Hello Chunho,

I have reviewed the schematic and it looks very good. I do have the following comments for your consideration.

Regards,

Jonathan

Hello Chunho,

By default the nWKRQ pin is driven High to 3.6V which is an internal rail derived from the VSUP supply so that it is active when the device is in Sleep Mode. So if it is left in the default configuration it does not need a pullup resistor.

However, it can be configured to be an open-drain type of pin to use a pullup resistor to the VIO rail by setting the nWKRQ_VOLTAGE bit (0x0800[19]) to "1".

Regards,

Jonathan

The MCU I/O voltage is 3.3V. You said that the nWKRQ drives with 3.6V, would it be okay to connect the nWKRQ pin directly to the MCU?Hello Chunho,

Most MCU's should be tolerant of 3.6V, but this would need to be verified for the specific MCU you are using. If the MCU is not tolerant of 3.6V, then this could be divided down with a couple of resistors or switched to the open-drain configuration requiring a pullup resistor to 3.3V.

Regards,

Jonathan