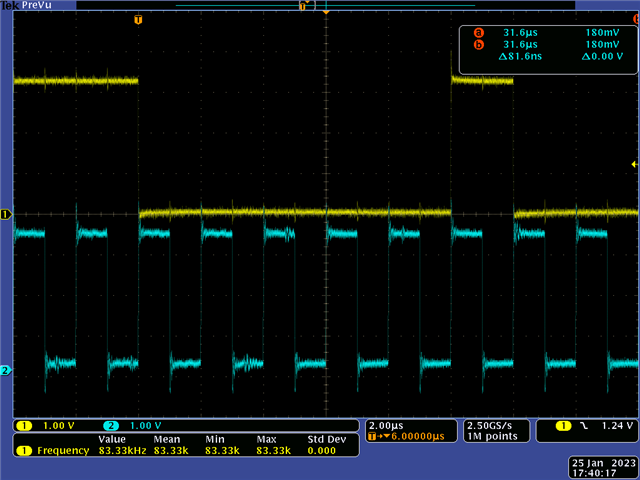

We are facing an issue while transmitting data. As per data sheet, when the external clock is used by the transmitter in pin IP3, the transmitted data is clocked on the falling edge of the clock. But our transmit data when probed on an oscilloscope shows the converse. Please see the attached scope image.

Also, we don't find a method in the datasheet to reverse the edge polarity. Why does this happen?

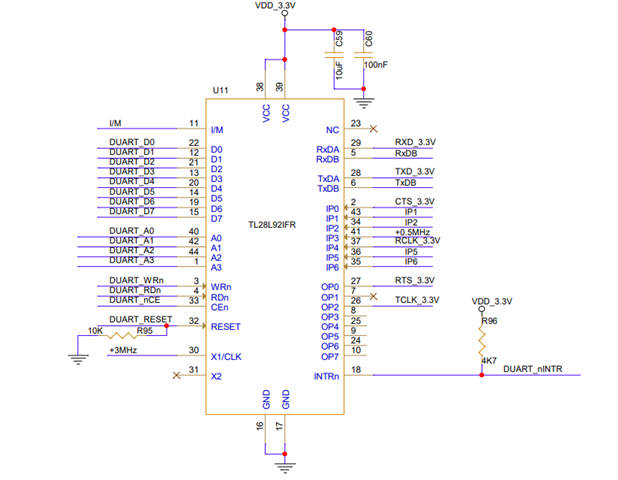

The DUART chip configuration is given below:

Normal mode

16 byte FIFO

interrupt when one or more bytes are received

disable watchdog

RxRTS control on

RxRDY interrupt enabled

block error mode

no parity

8 bits/char

normal channel mode

no TxRTS control

CTS enable of transmit

1 stop bit

receive clock = IP4 (1x)

transmit clock = IP3 (1x)

The DUART pin level details are attached.