Other Parts Discussed in Thread: DS160PT801

Previous E2E Case : https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1189931/ds160pt801x16evm-ds160pt801x16evm

Before read below my quesetion, Please read "Previous E2E Case" First.

It may help you understand my qeustion.

========================================================================

Part of Previous E2E Case

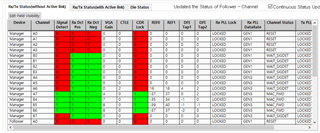

I can't see proper retimer(DS160PT801X16EVM) Gen3 performance with Gen3 NVMe.

Please check my test results and then give me feedback.

1. Test Environment

1) ubuntu PC : Intel(R) Core(TM) i9-10900 CPU, 64GB Memory PC

2) ubuntu Version : Ubuntu 18.04.6 LTS

3) Retimer : DS160PT801X16EVM

4) NVMe : Micron MVMe Gen3 x4. 21100AT M.2 SSD

2. My Three Test Cases

1) Direct NVMe connection through PCIe Slot : Main board <-> PCIe to M.2 convert board <-> NVMe

NVMe is normally recognized as PCIe Gen3(ASPM Disabled) and Good Stable performance

2) Use TI Retimer : Main board <-> TI retimer(DS160PT801X16EVM) <-> PCIe to M.2 convert board <-> NVMe

NVMe is normally recognized as PCIe Gen3(ASPM L1 Enabled) and But Unstable performance

3) Use TI Retimer(Force Gen2 in BIOS Setting) : Main board <-> TI retimer(DS160PT801X16EVM) <-> PCIe to M.2 convert board <-> NVMe

NVMe is recognized as PCIe Gen2 and Stable performance

========================================================================

<< My Question >>

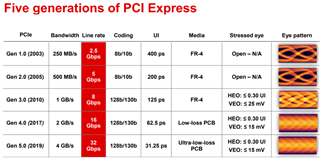

I found "PCIe Signal Integrity Challenges and Remedies" TI's doc.

In this doc. there are PCIe specification by generation.

gen3 needs HEO <= 0.3 UI and VEO <= 25mV

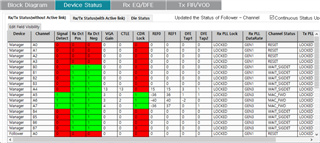

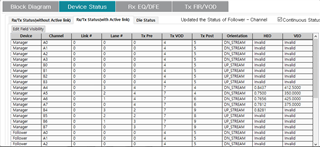

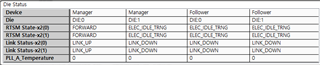

So. I checked HEO and VEO using SigCon Architect program.

I think HEO and VEO are higher than spec.

please review it.

Finally To improve the Gen3 throughput, What more should I check?

thanks,

hochang.