Part Number: TCA39306

TCA39305 support team

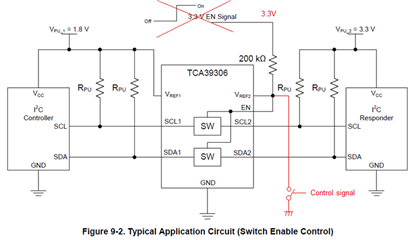

Figure 9-2 is recommended for controlling SW enable.

Is it possible to directly connect VREF2 and EN terminal to GND for SW control as shown below?

If NO, why is it?

Thanks

Tamio

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: TCA39306

TCA39305 support team

Figure 9-2 is recommended for controlling SW enable.

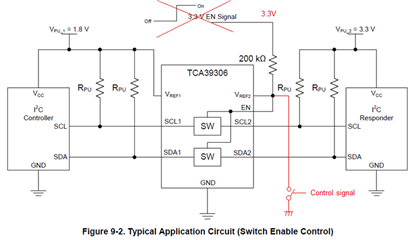

Is it possible to directly connect VREF2 and EN terminal to GND for SW control as shown below?

If NO, why is it?

Thanks

Tamio

Hi, Ladisch,

Do you mean that EN and VREF2 can be pulled down directly to GND without a resistor?

Isn't there any leakage current from VREF1 to VREF2?

Thanks

Tamio

EN is connected to the gates of all transistors. So when EN is low, there is no connection between VREF1 and VREF2.

Hey Tamio,

To further add on to Clemens' response- the I/O ports are also put into high impedance when the EN pin is driven low as well. As for the connection from the EN pin to GND, you can use an open drain driver as shown in a similar device here @0:55 mark.

Regards,

Jack

Hi, Ladisch, and Guan

I understood that SW can be disable by connecting EN pin to GND directly. And also, at the same time, can VREF2 connect to GND directly?

I think that VREF2 can connect to GND because I/O pin become Hi-Z at EN=LOW. Is my thought correct?

Thanks

Hi, Ladisch

I understood that there are no issue even if VREF2 and EN was directly connected to GND during VREF1=1.8V. "No issue" I say means no leakage current and no damage IC. So customer can use it for SW control.

Thanks