Part Number: SN65DSI84

Other Parts Discussed in Thread: DSI-TUNER,

Hi,

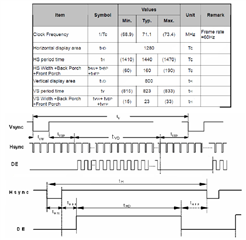

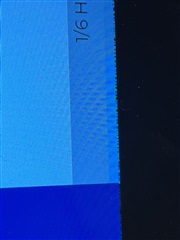

I have a flickering issue with my LVDS LCD panel

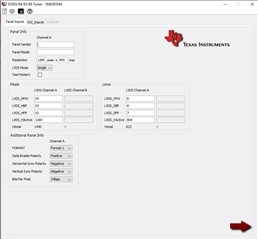

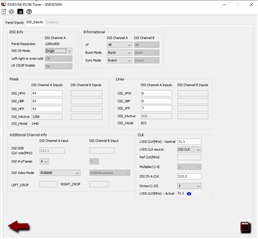

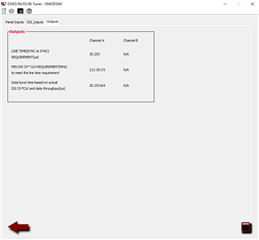

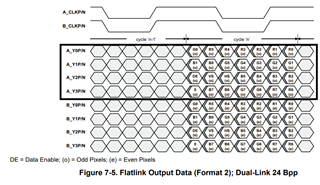

I follow the datasheet about sequence initilization and the DSI tuner to configure all the registers

Unfortunately, I still have the flickering issue

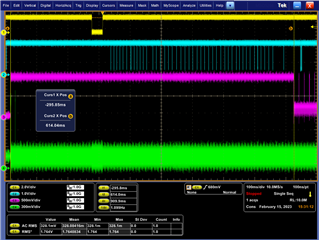

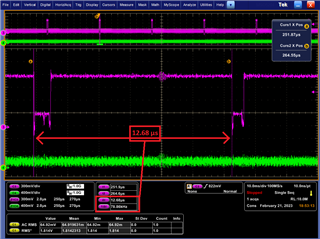

- Picture, 36:

CH3 = LVDS_DATA0CH4 = DSI_CLK

- Picture, 37 to 39

CH3 = LVDS_DATA0CH4 = DSI_DATA0