Hello TI,

I am working on a HDMI to LVDS bridge and have been slowly making progress based on your previous support, for which i want to say thank you.

I am currently at the stage where i am storing the EDID for my TFT resoluation and frequency etc on an EEprom which is read through the I2C bus when the hdmi source is connected. The Eeprom used is CAT24C208.

After connecting the HDMI source (my PC) to my board, the exchange of EDID is successful and the 'monitor' is detected and appears on my PC as having been detected and ready for display. My issue is however that regardless of this successful exchange of EDID there is still no image data being transmitted over the HDMI differential pairs, which tells me i am still missing something.

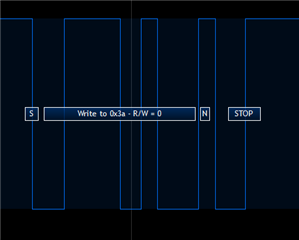

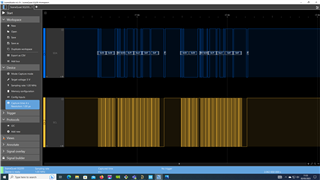

I measured the I2C bus on a different working AD board to observe what is occuring and noticed that after the EDID is transmitted there is some additional data that is sent to address 0x3A - after doing some research have i correctly identified this as being the HDCP? If so, why is HDCP necessary for my application?

Could you please advise me on what I need to do to get my computer to transmit video data to the Chip?

I have attached my EDID raw data that causes the PC to detect it as an external display, and i have also attached a waveform screenshot and file (use ScanaStudio to open https://www.ikalogic.com/scanastudio/ ) for your reference.

Thank you for any help,

Best Regards,

Kacper

r

r

00,FF,FF,FF,FF,FF,FF,00, 4A,8B,3B,2A,01,01,01,01, 17,15,01,03,80,3C,22,78, EA,1E,C5,AE,4F,34,B1,26, 0E,50,54,A5,4B,00,81,80, A9,40,D1,C0,71,4F,01,01, 01,01,01,01,01,01,28,3C, 80,A0,70,B0,23,40,30,20, 36,00,55,50,21,00,00,1E, 00,00,00,FF,00,4A,32,35, 37,4D,39,36,42,30,30,46, 4C,0A,00,00,00,FC,00,52, 54,4B,20,46,48,44,0A,20, 20,20,20,20,00,00,00,FD, 00,38,4C,1E,51,11,00,0A, 20,20,20,20,20,20,01,E1 0x80 Data 02,03,29,F1,50,90,05,04, 03,02,07,16,01,1F,12,13, 14,20,15,11,06,23,09,07, 07,67,03,0C,00,10,00,38, 2D,83,01,00,00,E3,05,03, 01,02,3A,80,18,71,38,2D, 40,58,2C,45,00,06,44,21, 00,00,1E,01,1D,80,18,71, 1C,16,20,58,2C,25,00,06, 44,21,00,00,9E,01,1D,00, 72,51,D0,1E,20,6E,28,55, 00,06,44,21,00,00,1E,8C, 0A,D0,8A,20,E0,2D,10,10, 3E,96,00,06,44,21,00,00, 18,00,00,00,00,00,00,00, 00,00,00,00,00,00,00,3E, Then reads device address 0x3A and regiter address 0x40 81,00,00,00, Then tries to read from 0x40 but only gets NACK and stops Then waits 333ms and reads 0x3A again