Part Number: SN65HVD72EVM

Other Parts Discussed in Thread: SN65HVD72

Hi Team,

Now I am conducting test on sn65hvd72EVM with sn65hvd72 soldered, finding the measured differential waveform is quite strange.

Two boards are connected together for simulating real transmission : One for sending and the other for receiving.

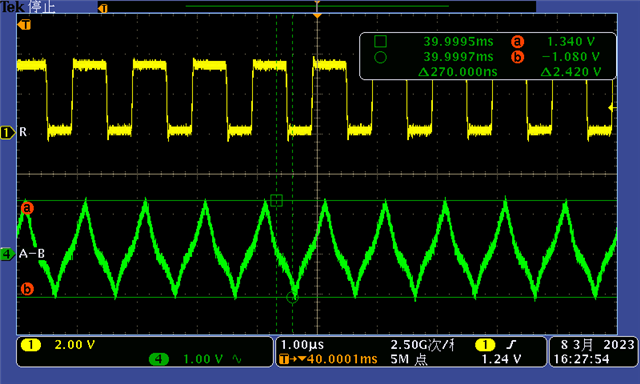

When sent data is 1MHz square waveform with 0V-3V, the measured differential waveform and receiving waveform are shown below:

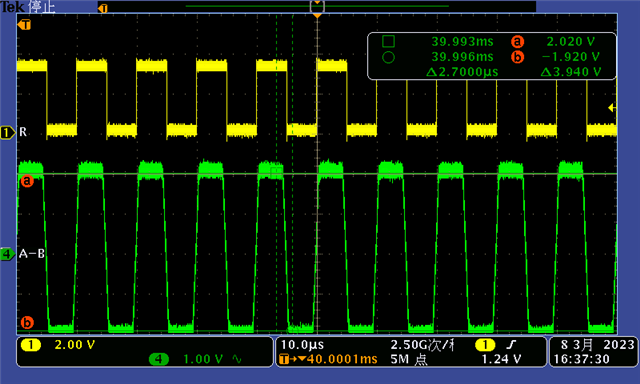

And when send data is 100kHz square waveform with 0V-3V, measured waveforms are shown below:

I have several questions about waveforms:

1. Why the differential waveform is not square when sent data is 1MHz?

2. Why the part could output 1MHz square waveform in receiver? Since sn65hvd72 could only support 250kps.

3. Why the amplitude varies with frequency?

BRs

Zixu