Part Number: DS90UB941AS-Q1

Other Parts Discussed in Thread: USB2ANY

We are currently debugging TI's serializer 941+deserializer 948 on the 8155 platform, but we have encountered some problems.

The specific problems are as follows:

At present, the serializer 941 can read and write registers normally, and the deserializer 948 device has appeared, which can also read and write I2C,

By checking the 948 register 0x1C, the serializer and deserializer have been locked.

The mipi clock of the platform is set to continuous mode, so the mipi clock has always been in hs mode, but the lvds screen at the 948 end of the screen has no content display.

Therefore, we request your technical support and ask some questions:

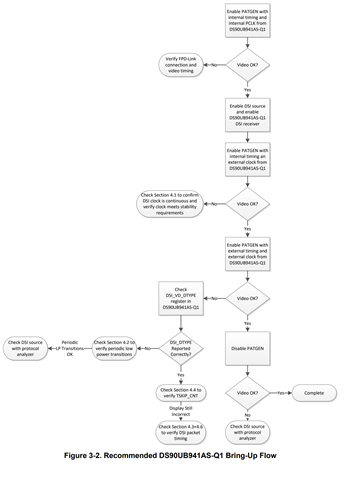

1. If there is a test mode, you can directly brush the screen to verify whether there is no problem with our hardware

2. The mipi of the platform is output to 941, and then to 948948 through FPD LINK to analyze the data, and finally to the lvds screen. Does this process necessarily require that the mipi of the platform must be

Hs clock, if mipi clock can be in continuous mode or non-continuous mode, do you need to set some registers of 948, and then let 948 solve continuous mode or non-continuous mode

3. The register manual we got is in English, which is obscure and difficult to understand. Many registers are not very clear. Is there any register manual or some data in Chinese, and the code annotation is easy to understand

If so, can you provide it for us to check