Hello Madam, Sir,

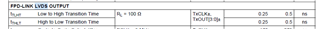

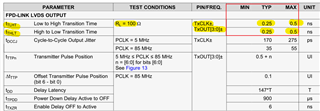

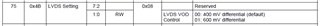

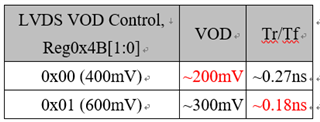

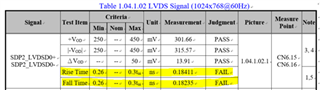

We found the rise/fall time of LVDS Data of DS90UB928 were faster than 0.26ns min. of LVDS spec, TIA/EIA-644-A, see Table.1, Fig.1 and Fig.2. Is there any way to make it slower? For example, to change to registry setting of DS90UB928 or DS90UB929?

Here is the display path of our system.

Intel Apollo Lake SoC -->(HDMI) --> DS90UB929TRGCTQ1 --> (FPD-LINK) --> DS90UB928QSQ/NOPB --> (LVDS) --> 10” LVDS panel

Thx!

Table.1

Fig.1

Fig.2