Part Number: DS90UB941AS-Q1

Hi team,

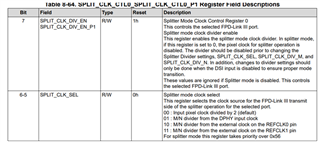

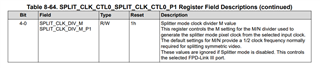

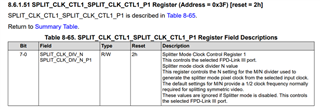

My customer couldn't turn on the screen stably when using 941Splitter Mode in the early stage, but he can turn on the screen stably after configuring the 0x3E and 0x3F registers. The configuration parameters are as follows:

{0x3E 0x15},

{0x3F 0x7C},

{0x3E 0xB5},

At present, the customer's two registers are not well understood, and I hope BU can answer them. Will there be other problems with the above configuration?