Part Number: SN75DP159

Hi,

Base on below E2e link. Our customer have add common mode choke.

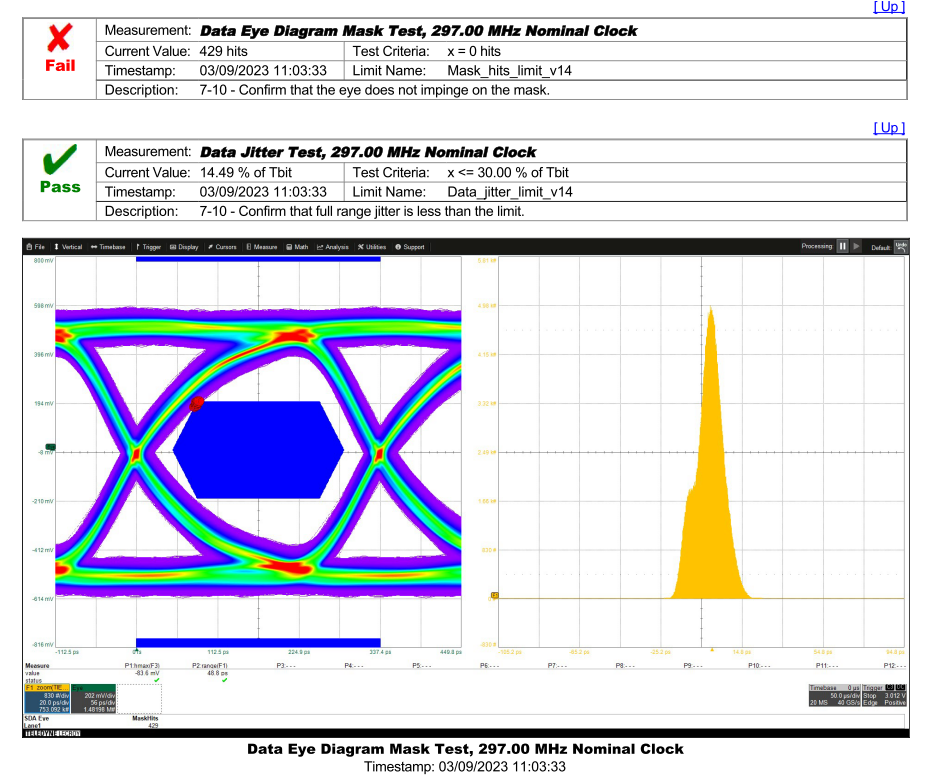

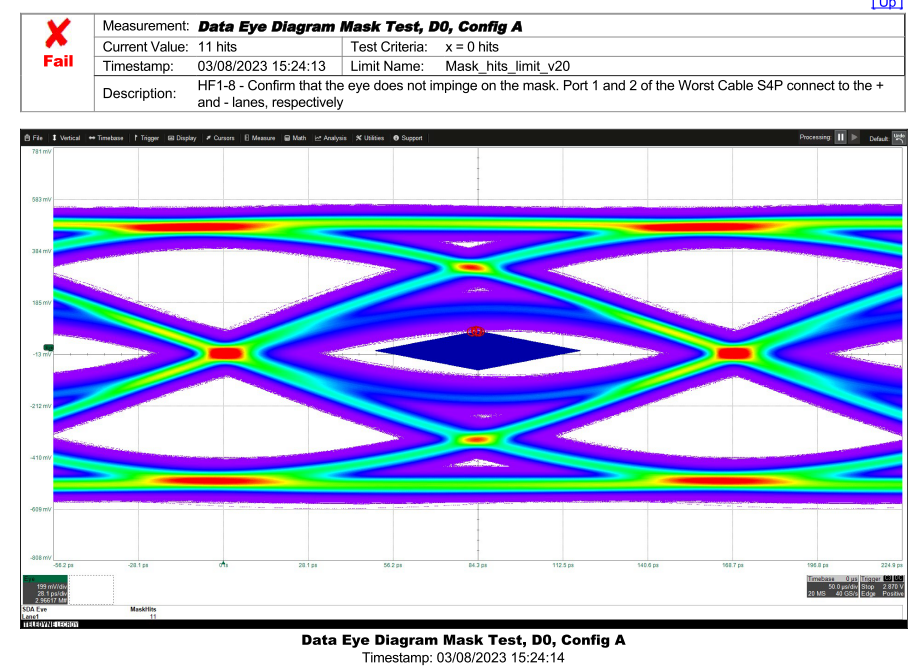

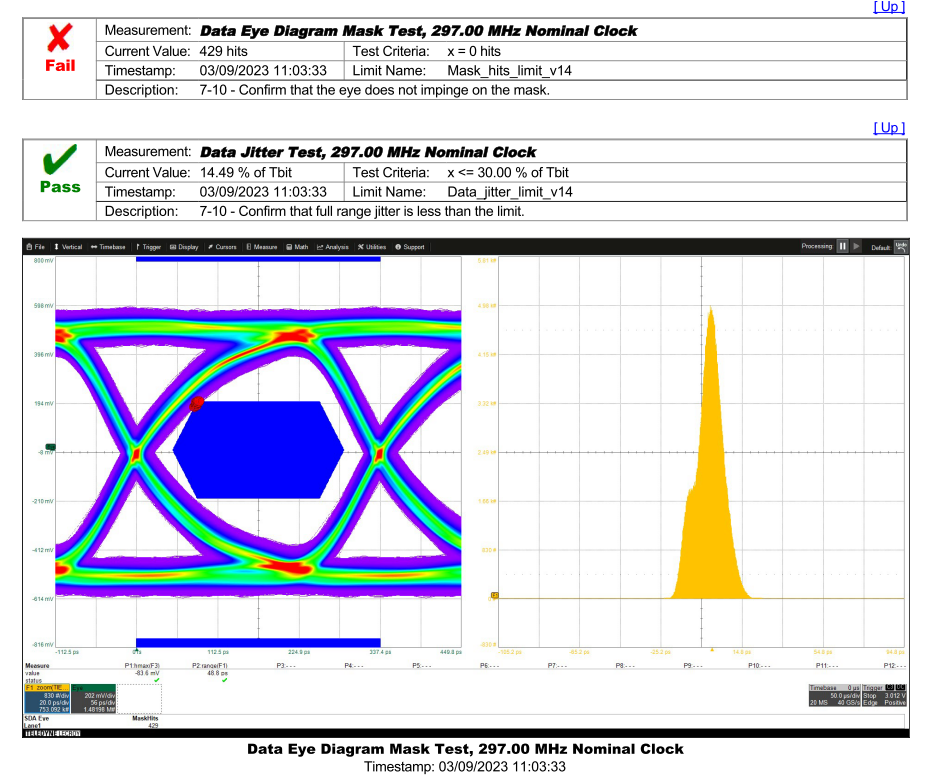

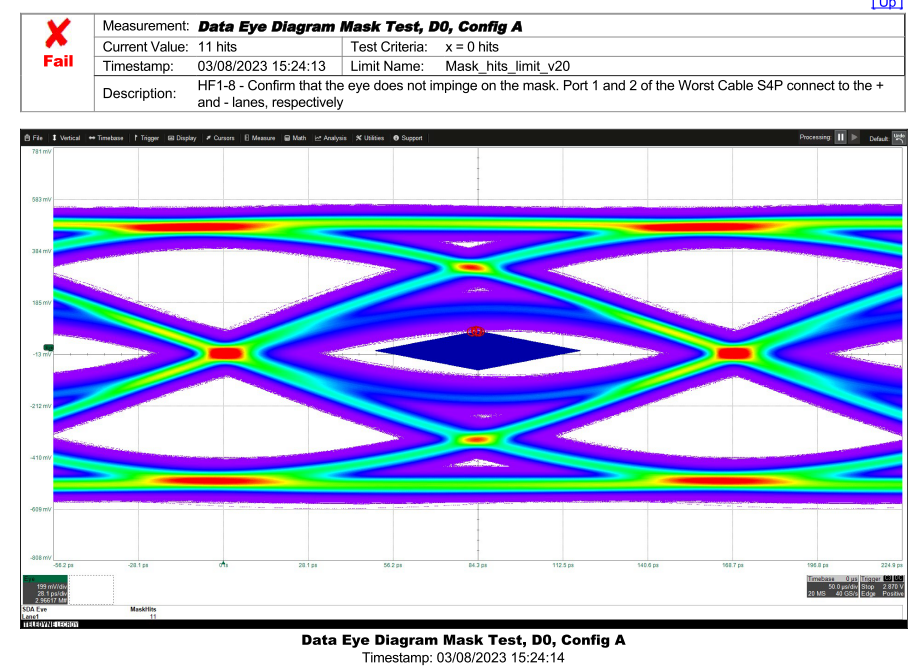

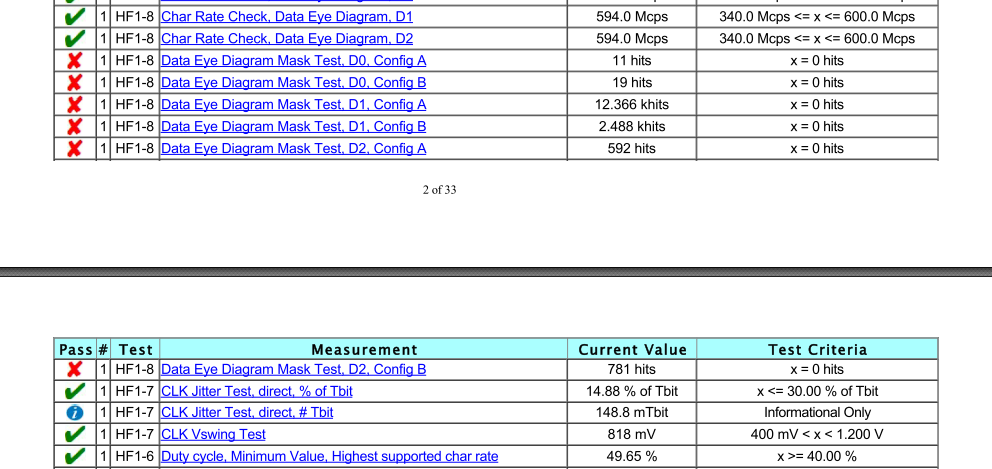

Now can pass intra-pair skew test. But have another Data Eye Diagram Fail.

Would you please suggest how to adjust EQ or slew?

Thanks!

Jeff

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: SN75DP159

Hi,

Base on below E2e link. Our customer have add common mode choke.

Now can pass intra-pair skew test. But have another Data Eye Diagram Fail.

Would you please suggest how to adjust EQ or slew?

Thanks!

Jeff

Jeff

Can you share the common mode part number? Does it have sufficient bandwidth?

Thanks

David

Jeff

The common mode choke datasheet does not specify the supported bandwidth. But given the description that it can support USB3.1 10G, I would assume it can support HDMI6G as well.

Can you also share their layout with me and let me review it?

Thanks

David

Hi Daivd,

I've pass schematic and layout file via privacy message.

Thanks!

Jeff

Jeff

Looking at the schematic, please note the configuration pin pullup/pulldown resistor requirement as shown below,

[3-Level Input pins]

Pull-up: 65k +/- 10%

Pull-down: 0 to 65k + 10%

[2-Level (LVCMOS) Input pins]

Pull-up: 0 to 65k + 10%

Pull-down: 0 to 65k + 10%

Since they have four DP159, are they seeing eye diagram failure on all of them, and every lane?

The output trace is short, and with 3Gbps data rate, I do not expect the loss to be an issue that will degrade the eye.

The ESD has a 0.5uF capacitance, can they switch to another ESD device that has lower capacitance that 0.5uF?

Thanks

David

Hi David,

What mean configuration pin pullup/pulldown resistor on [3-Level Input pins] and [2-Level (LVCMOS) Input pins]? In schematic which location?

Data eye test in HDMI all lane are failed.

ESD datasheet as below, seems spec is fine.

Nichtek_D2550-5R5_V.5_20210727 (1).pdf

Thanks!

Jeff

Jeff

This is the ESD I am looking at from their schematic, which is AZ1045-04F. The link to its datasheet indicated its line capacitance of 0.5pF. Are you saying that they are using a different ESD from the one in the schematic? Can you remove the ESD and see if there is an improvement in the eye diagram?

The DP159 datasheet pin definition lists which pin is 3-level and which is 2 level. For example, SLEW_CTL, PRE_SEL, and EQ_SEL are 3-level input which HDMI_SEL is a 2-level input pin.

Thanks

David

Hi David,

We are tried for remove ESD to check again, but some configuration pin pullup/pulldown resistor want double confirm with you again.

In this schematic is pullup/pulldown resistor is correct or not? need ant adjust?

Jeff

Please change the pullup on DPA_EQ, DPA_PRE, and DPA_SLEW to 65k. Please also remove the 1M pullup on DPA_OE_RST since DP159 already has an internal pullup.

Thanks

David