Part Number: DP83869HM

Hi,

Our board contains a FPGA and a DP83869HM PHY with SFP (RGMII to 1000Base-X).

On start-up, the PHY starts always OK. But after re-programming the FPGA, sometimes the PHY doesn't respond to the SMI bus.

On a MDIO read, I get always the same data (first data is random, all next data is the same as the first). It seems the PHY is frozen.

Only a power-cycle helps. The XI clock and Reset signal comes out the FPGA (hard-coded, not controllable) with a pull-down resistor.

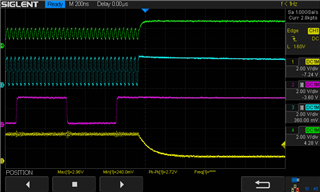

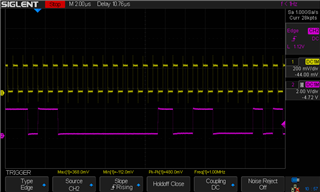

Some timing measurements:

- The XI clock is started 17ms before rising edge of HW_RESET.

- The MDC clock is continuously, started 34us after HW_RESET. The frequency is 1 MHz. (The first MDIO action is a long time later).

Thanks in advance,

Jacob