Part Number: TCA9802

Could you explan input leakage current of SDAA, SCLA ?

1. When VI = VCCA =0 , EN = GND

2. When VI >VCCA, EN = GND

3. When VI <VCCA, EN = GND

Will the leakage change when EN is connect to a very high resistance to GND?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: TCA9802

Could you explan input leakage current of SDAA, SCLA ?

1. When VI = VCCA =0 , EN = GND

2. When VI >VCCA, EN = GND

3. When VI <VCCA, EN = GND

Will the leakage change when EN is connect to a very high resistance to GND?

Hi Weilun,

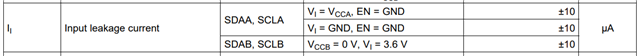

Your question is pulled from the electrical characteristics portion in the datasheet:

VI is the input voltage while EN is the voltage on the enable pin.

In all three cases, the internal buffer re-driving circuitry is turned off due to EN = GND.

Cases 1 and 3 should be about the same input leakage current between -10 uA and +10 uA. For case 2, we do not spec this in the datasheet. The device does have powered-off high impedance I2C bus pins on the A-side. So if a input voltage is present when VCCA < UVLO, it is safe to still have I2C communication present on the A-side.

Will the leakage change when EN is connect to a very high resistance to GND?

We also don't spec the leakage current here when EN in this specific scenario. I would expect the input leakage current on SDAA/SCLA/SDAB/SCLB to change very little, as this is the connection to a high-impedance input internally.

Regards,

Tyler

If want to put pull low resistor on EN pin, do you have any concern or suggestion?

Thank you very much.

Weilun,

The EN pin has a built in pull-up resistor (typical value of 250kohm) to VCCA. If you decide to tie EN to GND via pull-down resistor, you would need to make sure that the pull-down is stronger than 250k. A good value to start with would be something like 10kohm. This would ensure that you bias the EN pin to a low state by overcoming the internal pull-up.

Regards,

Tyler