Part Number: TCAN4550

Hi Jonathan,

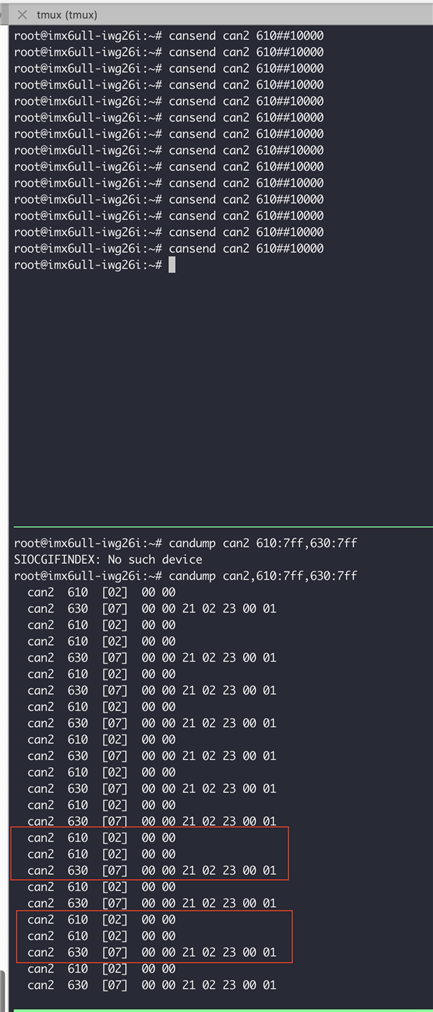

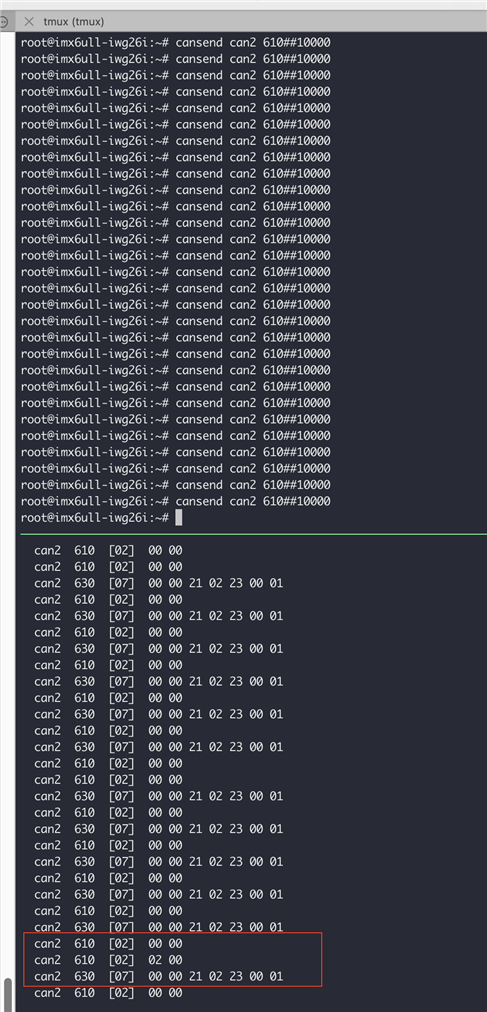

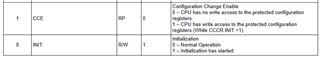

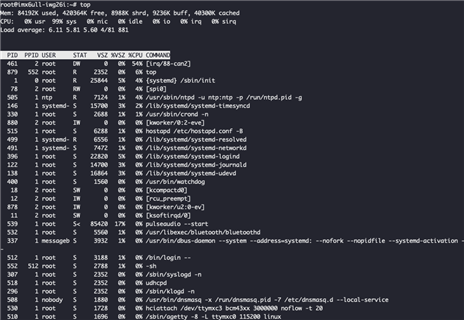

We have applied the patch which you had shared us and have started the testing. We are using <0x0 0 0 26 0 0 1 1> as our current mram-cfg. Since the size is limited to 2K bytes, we will not be able to use the earlier configuration <0x0 3 2 32 10 1 32 7> which is exceeding 2K byes. By using the current configuration we are not observing any upgrade in the performance.

So is there any other configuration which you would suggest us?

Regards,

Akshay Naik