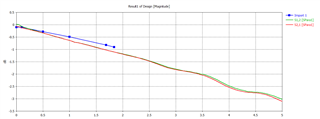

We are facing an issue that the insertion loss is failing for the FPD Link III IC (DS90UB928Q-Q1) during simulation in the CST tool. I have attached the snip for the failed insertion loss. We have to fix this issue in the layout. We are requesting the TI to give suggestion for the improvement in layout.