Part Number: DP83TG720S-Q1

HI TEAM

I have some power up questions for DP83TG720S

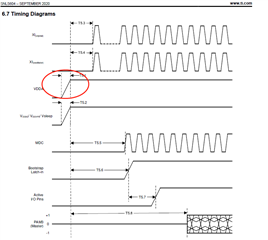

(1) for the VDDA power up timing, the minimum value of T5.1 is 0.5ms,however we measured it 0.039ms,so what risk will this cause?

I looked over all the power up timing questions, some expert indicate that it will cause some POR problem,and should HW RESET the phy to solve the problem?does it can solve my risk?

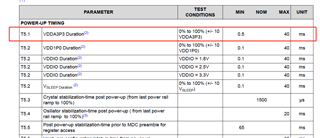

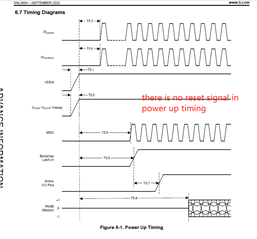

(2) in the power up timing ,there is no reset signal ,so ,when powered up, when can the reset singal can be low or high?

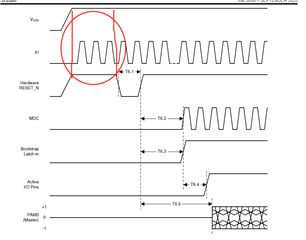

(3)in reset timing,we can get the T6.1, I wanner kown how long would it be take in the red circle part of reset timing in the followed figure

hope for your answer,thanks