Part Number: TCAN4550EVM

Other Parts Discussed in Thread: TCAN4550

Hi TI Team,

We are using TCAN4550 EVM with IMX8MN Nano EVK.

We are loading 3 drivers for TCAN4550 module.

1)insmod can-dev.ko

2)insmod m_can.ko

3)insmod tcan4x5x.ko

It is showing below mentioned error during tcan4x5x driver loading.

[ 35.106793] tcan4x5x spi1.0: no clock found

[ 35.111038] tcan4x5x spi1.0: no CAN clock source defined

[ 35.177749] tcan4x5x spi1.0: Unsupported version number: 0

[ 35.214917] tcan4x5x: probe of spi1.0 failed with error -22

Could you please guide us for unsupported version number issue.

Note – For TCAN EVM we are not providing clock. TCAN EVM has itself 40 MHz crystal clock.

Reference log

1) root@CT-100:~#

root@CT-100:~# insmod can-dev.ko

[ 22.982106] CAN device driver interface

root@CT-100:~#

root@CT-100:~# insmod m_can.ko

root@CT-100:~#

root@CT-100:~#

root@CT-100:~# insmod tcan4x5x.ko

[ 35.106793] tcan4x5x spi1.0: no clock found

[ 35.111038] tcan4x5x spi1.0: no CAN clock source defined

[ 35.177749] tcan4x5x spi1.0: Unsupported version number: 0

[ 35.214917] tcan4x5x: probe of spi1.0 failed with error -22

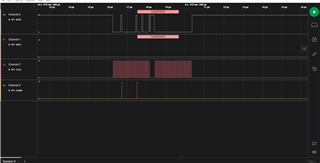

We are using below mentioned pins for hardware connection between TACN EVM and IMX8 Nano.

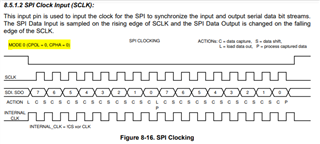

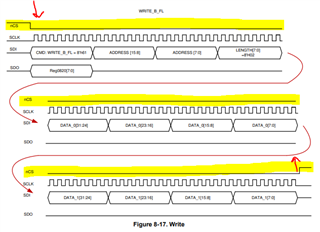

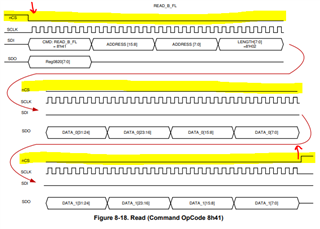

1)SDI

2)SDO

3)SCLK

4)RST

5)GPO1 / CLKOUT

6)nCS

7)nINT

8)GPO2

If any additional details are required, please let me know.

Regards

Ramji Mishra