Other Parts Discussed in Thread: DS125BR820, TDP1204, TMDS1204

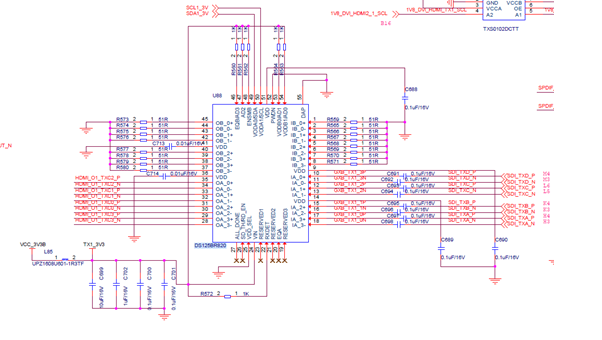

we use DS125BR820 as the redriver for HDMI2.1 TMDS/FRL output, the above picture is the SCH.

The main registers settings of DS125BR820 are in the following:

RDEXT = 0x08;

EQx = 0x00;

VOD = 0xa8+6;

VOD_DB = 0x00;

SD_TH = 0x00;

The inputs of DS125BR820 are the HDMI2.1 TMDS/FRL outputs which are from FPGA of Xilinx ZU7EV. And the outputs of DS125BR820 are as the "HDMI" Source.

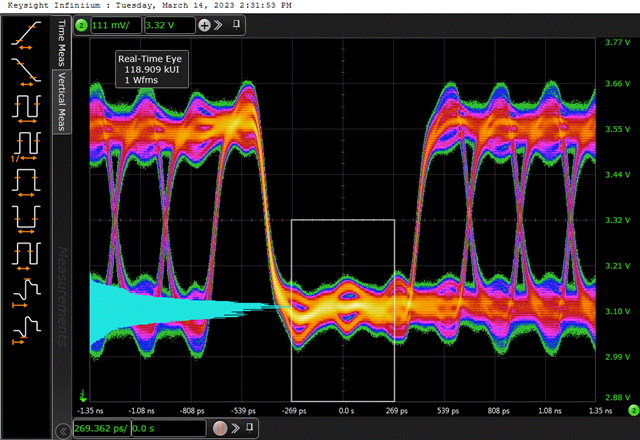

According to the TMDS principle, TMDS signals should be drived by the constant current source (10mA). Since at the SINK side of HDMI, the TMDS/FRL signals are pulled up to 3.3V with 50 ohms. If the TMDS siganls Vpp is 500mV, The high level of the normal output of TMDS should be 3.3V, while the lower level should be 2.8V.

Becasue DS125BR820 is also CML output, so the output should accord with the TMDS principle.

While in our outputs from DS125BR820. The high level of DS125BR820 output of TMDS is 3.55V, and the lower level is about 3.1V. please refer to the picture.

The questions: Are there any register settings or SCH problem of our DS125BR820? The level of TMDS from DS125BR820 in our application are different from the normal TMDS ouput, Why?

Thank you for your coming great support!