Simply put, shadow register is a register devised within the microcontroller for purpose of holding certain data to be used later. The name "Shadow" implies to duplicate some value and use it again - so it wont get lost.

https://electronics.stackexchange.com/questions/86032/what-actually-is-a-shadow-register

By the way, what do you think about following behavior ?

>My customer said that when write data to address 0x0000, it seems that same data will be applied to address 0x0C00 in case of using DP83869HM with rev A.

(Vice versa.)

From above, we have following question.

How do user distinglish standard register (0x0000) and extension(vendor define) register (0x0C00) ?

(Because, if user set address 0x0000 to something, same setting will be applied. in other words, I think user do not need to access extension(vendor define) register.)

Best Regards,

Other Parts Discussed in Thread: DP83869

Hello,

I would like to confirm difference between Rev A and Rev B of DP83869HM.

I understand that difference between these two is below.

* change design to fix occasional anomaly in fiber auto negtiation.

This means I understood TI only changed point which is related to fiber auto negotiation.

However, I found following difference.

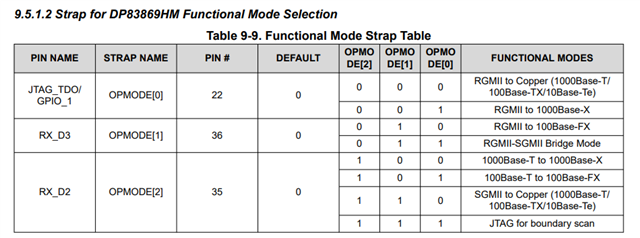

1. Setting for "RGMII to 1000Base-X" is changed.

According to datasheet Rev B, there is following description on "RGMII-to-1000Base-X Mode".

• Write 0x0041 to register 1DFh // Set Operation Mode to RGMII to 1000Base-X

• Write 0x1140 to register C00h // Reset FX_CTRL

• Write 0x4000 to register 1Fh// Software Reset

On the other hands, in case of datasheet Rev A, there is following description on "RGMII-to-1000Base-X Mode".

After configuring register 0x01DF, perform the following operations.

• Write 0x1140 to register 0x0000

The register access is added in Rev B.

And register which TI require to write 0x1140 is changed from 0x0000 to 0xC00.

2. Address 0x1EC, 0xC09 and 0xC10 are disclosed at datasheet Rev B.

Then I have following questions.

Q1. Even if user use Rev A version of DP83869HM device, do user need to follow description of datasheet Rev B when they use "RGMII to 1000Base-X" mode ?

Q2. If user use Rev A version of DP83869HM device, can user also access registers which I described above "2" ?

Is it added on Rev B version of DP83869HM only or TI just mistake datasheet Rev A description (just change typo) ?

Best Regards,