HI

I am now using TUSB1210.

Clock is input of TUSB1210.

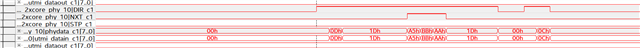

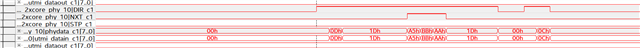

If connected to FPGA, TUSB i/0 looks like below.

which is not matched protocol.

datain is input of FPGA.

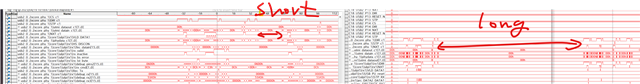

now DIR is too long , and even start before NXT

How to fix this ?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

HI

I am now using TUSB1210.

Clock is input of TUSB1210.

If connected to FPGA, TUSB i/0 looks like below.

which is not matched protocol.

datain is input of FPGA.

now DIR is too long , and even start before NXT

How to fix this ?

Sorry, we can not sent RTL model to customer.

which FPGA you are going to use?

Regards

Brian

using Intel stratix10.

the problem is DIR/NXT is input of FPGA, i.e output TI PHy chip.

FPGA just send clock and reset to PHY chip.

PHY chip try to check there is device or not ( link or not..)

In this time. DIR/NXT timing is not same as Ulti protocol.

that is the issue at now

how to resolve it ? need help.

Great. but I still wonder that FPGA only send out CLK/RESET/DATA/STP to PHY.

1) Which signals can make PHY thinks got errors ?

2) Even FPGA send out 8'h4B with STP

sometimes USB analyzer shows can detect device but sometimes not.

What is correct output from FPGA to PHY for windows recognized there is USB device ?

Thanks

Ok.

1 ) If PHY receive, RXError how to resolve it ?

2)

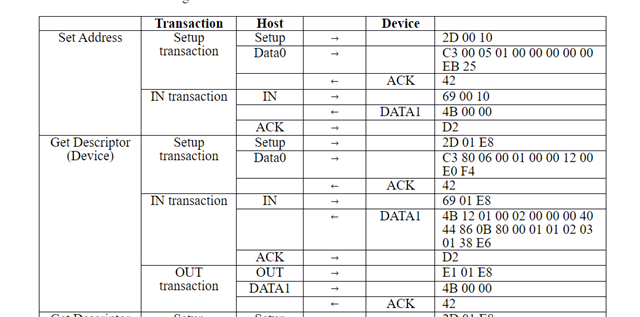

For enumeration stage,

I think PHY should act like this,

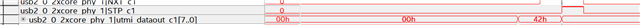

yes , sometimes I can see. but as u can see my waveform from FPGA,

2D0010 --> C38006000100004000DD94.

in this case DATA0 is C3 80 06 ....

but I think should be

|

Data0 |

→

|

|

C3 00 05 01 00 00 00 00 00 EB 25

|

in this case, DATA0 is matched.

My question is Why PHY send out different DATA0 ?

How can I obtain DATA0 from PHY ?

Can I get Behavior mode/ description after get reset /clock from outside ?

After reset, PHY should send out DIR/NXT to FPGA.. but in my case, I still don't know what is expected from PHY.

With that, I can check board design something.. but as u can DIR always high in my case ( it mean there are errors.. but why ?

which error? how to resolve ? how to clear it ?

is this device application? do you have ulpi wrapper for this FPGA model?

Regards

Brian

our FPGA board has FPGA chip + TUSB1210 chip.

and inside FPGA, I have USB device RTL code.

so Device ( FPGA ) <--> TUSB1210 in a single board .

Device input signal was shared to u.

so what is expectation from TUSB1210 ?

I think it try send out DIR/NXT periodic. but I don't know what is output for TUSB1210.

and what is expected signals in TUSB1210 from FPGA

Can I look at your schematic?

For USB device, no driver needed. It's enough if you have device RTL code.

Regards

Brian

After got ACK, PHY should send In transition in.

but there are gap between left and right one.

Why pHy behaviors is different ?