Hi Team,

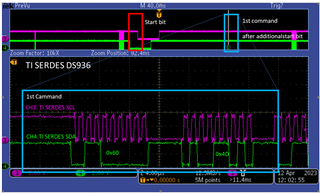

We found that the 936 I2C port has some countermeasure when there is a start bit, but no following action.

Please see below image. You can see there is I2C start bit in the middle of upper window. And then we continuously sent the I2C command and 936 can receive it.(Ack)

But we found some chips may miss the command. May you share the mechanism about why our 936 can also receive the I2C command even though there is start bit before it?(Maybe we have I2C timeout?) Thank you.

Regards,

Roy