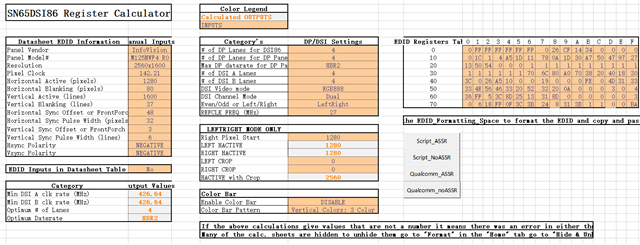

Part Number: SN65DSI86

Hi Ti,

1. We plan to replace the panel with a resolution of 2.8k, and the parameters are:

2880*1800, 24bit, @60Hz, sn65dsi86 can support this resolution?

2. What is the maximum resolution supported by sn65dsi86? How do you calculate it?