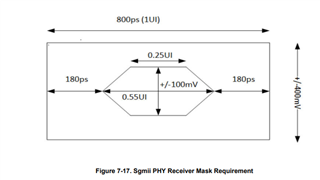

The TX is aligned, trace cap with ILA in my fpga, proper k chars are coming in with no apparent violations - appears to be the periodic configuration from my mac layer. The RX however, does not appear to be synchronized and from my sampling I saw multiple groups of more than 5 1's together, which tells me asynch. In 4-wire mode the SGMII interface in the SERDES must latch onto the RX data in order to synchronize. I wanted to rule out the PHY first however - and I wanted to ensure the configuration is occurring correctly before moving on.

Please advise:

(lazy dump at the end of current configuration)

Reg: 0x0000, Value: 0x0140

Reg: 0x0001, Value: 0x7949

Reg: 0x0002, Value: 0x2000

Reg: 0x0003, Value: 0xA231

Reg: 0x0004, Value: 0x01E1

Reg: 0x0005, Value: 0x0000

Reg: 0x0006, Value: 0x0064

Reg: 0x0007, Value: 0x2001

Reg: 0x0008, Value: 0x0000

Reg: 0x0009, Value: 0x1300

Reg: 0x000A, Value: 0x0000

Reg: 0x000B, Value: 0x0000

Reg: 0x000C, Value: 0x0000

Reg: 0x000D, Value: 0x401F

Reg: 0x000E, Value: 0x1030

Reg: 0x000F, Value: 0x3000

Reg: 0x0010, Value: 0x5C48

Reg: 0x0011, Value: 0xA802

Reg: 0x0012, Value: 0x0000

Reg: 0x0013, Value: 0x0000

Reg: 0x0014, Value: 0x29C7

Reg: 0x0015, Value: 0x0000

Reg: 0x0016, Value: 0x0000

Reg: 0x0017, Value: 0x0040

Reg: 0x0018, Value: 0x6150

Reg: 0x0019, Value: 0x4440

Reg: 0x001A, Value: 0x0002

Reg: 0x001B, Value: 0x0000

Reg: 0x001C, Value: 0x0000

Reg: 0x001D, Value: 0x0000

Reg: 0x001E, Value: 0x0002

Reg: 0x001F, Value: 0x0000

Reg: 0x0020, Value: 0x5668

Reg: 0x0021, Value: 0x5814

Reg: 0x0022, Value: 0x0718

Reg: 0x0023, Value: 0x8D1C

Reg: 0x0024, Value: 0xF01E

Reg: 0x0025, Value: 0x0400

Reg: 0x0026, Value: 0x008D

Reg: 0x0027, Value: 0xF810

Reg: 0x0028, Value: 0xFF80

Reg: 0x0029, Value: 0x0000

Reg: 0x002A, Value: 0x0000

Reg: 0x002B, Value: 0x0100

Reg: 0x002C, Value: 0x141F

Reg: 0x002D, Value: 0x0000

Reg: 0x002E, Value: 0x0221

Reg: 0x002F, Value: 0x0000

Reg: 0x0030, Value: 0x0000

Reg: 0x0031, Value: 0x1030

Reg: 0x0032, Value: 0x0000

Reg: 0x0033, Value: 0x0000

Reg: 0x0034, Value: 0x0000

Reg: 0x0035, Value: 0x0000

Reg: 0x0036, Value: 0x0000

Reg: 0x0037, Value: 0x0000

Reg: 0x0038, Value: 0x0000

Reg: 0x0039, Value: 0x0000

Reg: 0x003A, Value: 0x0000

Reg: 0x003B, Value: 0x0000

Reg: 0x003C, Value: 0x0000

Reg: 0x003D, Value: 0x0000

Reg: 0x003E, Value: 0x0000

Reg: 0x003F, Value: 0x0000

Reg: 0x0040, Value: 0x0073

Reg: 0x0041, Value: 0x0000

Reg: 0x0042, Value: 0x0000

Reg: 0x0043, Value: 0x07A0

Reg: 0x0044, Value: 0x0000

Reg: 0x0045, Value: 0x0000

Reg: 0x0046, Value: 0x0000

Reg: 0x0047, Value: 0x0000

Reg: 0x0048, Value: 0x0000

Reg: 0x0049, Value: 0x0000

Reg: 0x004A, Value: 0x0000

Reg: 0x004B, Value: 0x0000

Reg: 0x004C, Value: 0x0400

Reg: 0x004D, Value: 0x0055

Reg: 0x004E, Value: 0x0000

Reg: 0x004F, Value: 0x0210

Reg: 0x0050, Value: 0x0453

Reg: 0x0051, Value: 0x9ADA

Reg: 0x0052, Value: 0x01F4

Reg: 0x0053, Value: 0x2055

Reg: 0x0054, Value: 0x0000

Reg: 0x0055, Value: 0x0000

Reg: 0x0056, Value: 0x0000

Reg: 0x0057, Value: 0x0000

Reg: 0x0058, Value: 0x0000

Reg: 0x0059, Value: 0x0000

Reg: 0x005A, Value: 0x0000

Reg: 0x005B, Value: 0x0000

Reg: 0x005C, Value: 0x0000

Reg: 0x005D, Value: 0x0000

Reg: 0x005E, Value: 0x0000

Reg: 0x005F, Value: 0x0000

Reg: 0x0060, Value: 0x0008

Reg: 0x0061, Value: 0x0000

Reg: 0x0062, Value: 0x0001

Reg: 0x0063, Value: 0x0000

Reg: 0x0064, Value: 0x8000

Reg: 0x0065, Value: 0x43AA

Reg: 0x0066, Value: 0x2334

Reg: 0x0067, Value: 0x03E8

Reg: 0x0068, Value: 0x0000

Reg: 0x0069, Value: 0x0020

Reg: 0x006A, Value: 0x0000

Reg: 0x006B, Value: 0x0000

Reg: 0x006C, Value: 0x0289

Reg: 0x006D, Value: 0x8912

Reg: 0x006E, Value: 0x8884

Reg: 0x006F, Value: 0x0100

Reg: 0x0070, Value: 0x0000

Reg: 0x0071, Value: 0x0000

Reg: 0x0072, Value: 0x0000

Reg: 0x0073, Value: 0x0000

Reg: 0x0074, Value: 0x0000

Reg: 0x0075, Value: 0x0000

Reg: 0x0076, Value: 0x0000

Reg: 0x0077, Value: 0x0000

Reg: 0x0078, Value: 0x05ED

Reg: 0x0079, Value: 0x003F

Reg: 0x007A, Value: 0x0000

Reg: 0x007B, Value: 0x05DC

Reg: 0x007C, Value: 0x007D

Reg: 0x007D, Value: 0x0003

Reg: 0x007E, Value: 0x0000

Reg: 0x007F, Value: 0x0000

Reg: 0x0080, Value: 0x0000

Reg: 0x0081, Value: 0x0000

Reg: 0x0082, Value: 0x4E73

Reg: 0x0083, Value: 0x7FF2

Reg: 0x0084, Value: 0x0000

Reg: 0x0085, Value: 0x007E

Reg: 0x0086, Value: 0x0077

Reg: 0x0087, Value: 0x0000

Reg: 0x0088, Value: 0x03FF

Reg: 0x0089, Value: 0x8000

Reg: 0x008A, Value: 0x0000

Reg: 0x008B, Value: 0x0999

Reg: 0x008C, Value: 0x9999

Reg: 0x008D, Value: 0x0000

Reg: 0x008E, Value: 0x0010

Reg: 0x008F, Value: 0x0000

Reg: 0x0090, Value: 0x0000

Reg: 0x0091, Value: 0x0210

Reg: 0x0092, Value: 0x0210

Reg: 0x0093, Value: 0xBBBB

Reg: 0x0094, Value: 0x0000

Reg: 0x0095, Value: 0x0000

Reg: 0x0096, Value: 0x0000

Reg: 0x0097, Value: 0x0000

Reg: 0x0098, Value: 0x0000

Reg: 0x0099, Value: 0x4000

Reg: 0x009A, Value: 0x0285

Reg: 0x009B, Value: 0x0285

Reg: 0x009C, Value: 0x0000

Reg: 0x009D, Value: 0x0000

Reg: 0x009E, Value: 0x0000

Reg: 0x009F, Value: 0xBBBB

Reg: 0x00A0, Value: 0x0707

Reg: 0x00A1, Value: 0x0507

Reg: 0x00A2, Value: 0x1010

Reg: 0x00A3, Value: 0x1010

Reg: 0x00A4, Value: 0x0000

Reg: 0x00A5, Value: 0x8888

Reg: 0x00A6, Value: 0x0703

Reg: 0x00A7, Value: 0xFFFF

Reg: 0x00A8, Value: 0x0000

Reg: 0x00A9, Value: 0x0000

Reg: 0x00AA, Value: 0x0000

Reg: 0x00AB, Value: 0x4444

Reg: 0x00AC, Value: 0x4444

Reg: 0x00AD, Value: 0x010B

Reg: 0x00AE, Value: 0x0109

Reg: 0x00AF, Value: 0x0000

Reg: 0x00B0, Value: 0x0000

Reg: 0x00B1, Value: 0x0000

Reg: 0x00B2, Value: 0x0000

Reg: 0x00B3, Value: 0x0088

Reg: 0x00B4, Value: 0x0000

Reg: 0x00B5, Value: 0x1020

Reg: 0x00B6, Value: 0x1020

Reg: 0x00B7, Value: 0x0000

Reg: 0x00B8, Value: 0x0000

Reg: 0x00B9, Value: 0x0000

Reg: 0x00BA, Value: 0x7777

Reg: 0x00BB, Value: 0x0000

Reg: 0x00BC, Value: 0x0000

Reg: 0x00BD, Value: 0x0000

Reg: 0x00BE, Value: 0x0000

Reg: 0x00BF, Value: 0x0000

Reg: 0x00C0, Value: 0x0000

Reg: 0x00C1, Value: 0x0000

Reg: 0x00C2, Value: 0x0000

Reg: 0x00C3, Value: 0x0000

Reg: 0x00C4, Value: 0x1F1F

Reg: 0x00C5, Value: 0x0003

Reg: 0x00C6, Value: 0x0000

Reg: 0x00C7, Value: 0x0000

Reg: 0x00C8, Value: 0x0000

Reg: 0x00C9, Value: 0x7000

Reg: 0x00CA, Value: 0x0000

Reg: 0x00CB, Value: 0x0FBF

Reg: 0x00CC, Value: 0x2300

Reg: 0x00CD, Value: 0x0000

Reg: 0x00CE, Value: 0xE800

Reg: 0x00CF, Value: 0x3E00

Reg: 0x00D0, Value: 0x0000

Reg: 0x00D1, Value: 0x0000

Reg: 0x00D2, Value: 0x0002

Reg: 0x00D3, Value: 0x0000

Reg: 0x00D4, Value: 0x0E00

Reg: 0x00D5, Value: 0x8390

Reg: 0x00D6, Value: 0x0000

Reg: 0x00D7, Value: 0x0300

Reg: 0x00D8, Value: 0x0000

Reg: 0x00D9, Value: 0x0000

Reg: 0x00DA, Value: 0x0000

Reg: 0x00DB, Value: 0x0010

Reg: 0x00DC, Value: 0x3800

Reg: 0x00DD, Value: 0x0200

Reg: 0x00DE, Value: 0x0000

Reg: 0x00DF, Value: 0x0000

Reg: 0x00E0, Value: 0x3220

Reg: 0x00E1, Value: 0x30C0

Reg: 0x00E2, Value: 0x7A56

Reg: 0x00E3, Value: 0x204B

Reg: 0x00E4, Value: 0x0000

Reg: 0x00E5, Value: 0x0231

Reg: 0x00E6, Value: 0x0231

Reg: 0x00E7, Value: 0x0C83

Reg: 0x00E8, Value: 0x9696

Reg: 0x00E9, Value: 0x9F22

Reg: 0x00EA, Value: 0x2040

Reg: 0x00EB, Value: 0x0501

Reg: 0x00EC, Value: 0x190D

Reg: 0x00ED, Value: 0x6432

Reg: 0x00EE, Value: 0xFA96

Reg: 0x00EF, Value: 0x1840

Reg: 0x00F0, Value: 0x3E25

Reg: 0x00F1, Value: 0x6004

Reg: 0x00F2, Value: 0x0000

Reg: 0x00F3, Value: 0x0000

Reg: 0x00F4, Value: 0x6791

Reg: 0x00F5, Value: 0x199A

Reg: 0x00F6, Value: 0x1027

Reg: 0x00F7, Value: 0x051C

Reg: 0x00F8, Value: 0x1027

Reg: 0x00F9, Value: 0xAC76

Reg: 0x00FA, Value: 0x3033

Reg: 0x00FB, Value: 0x3104

Reg: 0x00FC, Value: 0x0067

Reg: 0x00FD, Value: 0x199A

Reg: 0x00FE, Value: 0xE721

Reg: 0x00FF, Value: 0x1027

Reg: 0x0100, Value: 0x0140

Reg: 0x0101, Value: 0x7949

Reg: 0x0102, Value: 0x2000

Reg: 0x0103, Value: 0xA231

Reg: 0x0104, Value: 0x01E1

Reg: 0x0105, Value: 0x0000

Reg: 0x0106, Value: 0x0064

Reg: 0x0107, Value: 0x2001

Reg: 0x0108, Value: 0x0000

Reg: 0x0109, Value: 0x1300

Reg: 0x010A, Value: 0x0000

Reg: 0x010B, Value: 0x0000

Reg: 0x010C, Value: 0x0000

Reg: 0x010D, Value: 0x401F

Reg: 0x010E, Value: 0x0000

Reg: 0x010F, Value: 0x3000

Reg: 0x0110, Value: 0x5C48

Reg: 0x0111, Value: 0xA802

Reg: 0x0112, Value: 0x0000

Reg: 0x0113, Value: 0x0040

Reg: 0x0114, Value: 0x29C7

Reg: 0x0115, Value: 0x0000

Reg: 0x0116, Value: 0x0000

Reg: 0x0117, Value: 0x0040

Reg: 0x0118, Value: 0x6150

Reg: 0x0119, Value: 0x4440

Reg: 0x011A, Value: 0x0002

Reg: 0x011B, Value: 0x0000

Reg: 0x011C, Value: 0x0000

Reg: 0x011D, Value: 0x0000

Reg: 0x011E, Value: 0x0002

Reg: 0x011F, Value: 0x0000

Reg: 0x0120, Value: 0x5668

Reg: 0x0121, Value: 0x5814

Reg: 0x0122, Value: 0x0718

Reg: 0x0123, Value: 0x8D1C

Reg: 0x0124, Value: 0xF01E

Reg: 0x0125, Value: 0x0400

Reg: 0x0126, Value: 0x008D

Reg: 0x0127, Value: 0xF810

Reg: 0x0128, Value: 0xFF80

Reg: 0x0129, Value: 0x0000

Reg: 0x012A, Value: 0x0000

Reg: 0x012B, Value: 0x0100

Reg: 0x012C, Value: 0x141F

Reg: 0x012D, Value: 0x0000

Reg: 0x012E, Value: 0x0221

Reg: 0x012F, Value: 0x0000

Reg: 0x0130, Value: 0x0000

Reg: 0x0131, Value: 0x1030

Reg: 0x0132, Value: 0x0000

Reg: 0x0133, Value: 0x0000

Reg: 0x0134, Value: 0x0000

Reg: 0x0135, Value: 0x0000

Reg: 0x0136, Value: 0x0000

Reg: 0x0137, Value: 0x0000

Reg: 0x0138, Value: 0x0000

Reg: 0x0139, Value: 0x0000

Reg: 0x013A, Value: 0x0000

Reg: 0x013B, Value: 0x0000

Reg: 0x013C, Value: 0x0000

Reg: 0x013D, Value: 0x0000

Reg: 0x013E, Value: 0x0000

Reg: 0x013F, Value: 0x0000

Reg: 0x0140, Value: 0x0073

Reg: 0x0141, Value: 0x0000

Reg: 0x0142, Value: 0x0000

Reg: 0x0143, Value: 0x07A0

Reg: 0x0144, Value: 0x0000

Reg: 0x0145, Value: 0x0000

Reg: 0x0146, Value: 0x0000

Reg: 0x0147, Value: 0x0000

Reg: 0x0148, Value: 0x0000

Reg: 0x0149, Value: 0x0000

Reg: 0x014A, Value: 0x0000

Reg: 0x014B, Value: 0x0000

Reg: 0x014C, Value: 0x0400

Reg: 0x014D, Value: 0x0000

Reg: 0x014E, Value: 0x0000

Reg: 0x014F, Value: 0x0270

Reg: 0x0150, Value: 0x0453

Reg: 0x0151, Value: 0x9ADA

Reg: 0x0152, Value: 0x01F4

Reg: 0x0153, Value: 0x2055

Reg: 0x0154, Value: 0x0000

Reg: 0x0155, Value: 0x0000

Reg: 0x0156, Value: 0x0000

Reg: 0x0157, Value: 0x0000

Reg: 0x0158, Value: 0x0000

Reg: 0x0159, Value: 0x0000

Reg: 0x015A, Value: 0x0000

Reg: 0x015B, Value: 0x0000

Reg: 0x015C, Value: 0x0000

Reg: 0x015D, Value: 0x0000

Reg: 0x015E, Value: 0x0000

Reg: 0x015F, Value: 0x0000

Reg: 0x0160, Value: 0x0008

Reg: 0x0161, Value: 0x0000

Reg: 0x0162, Value: 0x0001

Reg: 0x0163, Value: 0x0000

Reg: 0x0164, Value: 0x8000

Reg: 0x0165, Value: 0x43AA

Reg: 0x0166, Value: 0x2334

Reg: 0x0167, Value: 0x03E8

Reg: 0x0168, Value: 0x0000

Reg: 0x0169, Value: 0x0020

Reg: 0x016A, Value: 0x0000

Reg: 0x016B, Value: 0x0000

Reg: 0x016C, Value: 0x0289

Reg: 0x016D, Value: 0x8912

Reg: 0x016E, Value: 0x8884

Reg: 0x016F, Value: 0x0100

Reg: 0x0170, Value: 0x0000

Reg: 0x0171, Value: 0x0000

Reg: 0x0172, Value: 0x0000

Reg: 0x01D5, Value: 0x8390