Part Number: PCA9535

Hi team,

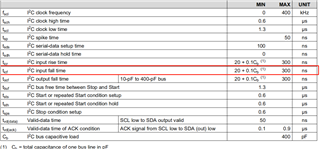

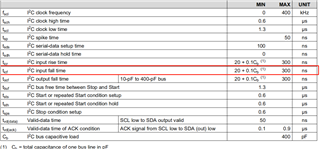

From datasheet, there is clear spec requirement of I2C input rise and fall time. If the I2C fall and rise time is out of spec, what risk will have? Thanks!

BR

Jiawei

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: PCA9535

Hi team,

From datasheet, there is clear spec requirement of I2C input rise and fall time. If the I2C fall and rise time is out of spec, what risk will have? Thanks!

BR

Jiawei

These values are copied from the I²C specification. The actual requirements of the PCA9535 itself are likely to be much looser.

If the rise/fall time is shorter than the specified minimum, there might be ringing on the bus, which will look like multiple clock pulses. If the rise/fall time is too long, you will not be able to reach 400 kHz.

Hi Jiawei,

The rise time and fall time specifications listed in the I2C standard are put in place so that I2C communication can be accurate across bus loading and different data rates across any system. These are general guidelines for system applications, and help to prevent different signal integrity issues that result from many different things such as ringing from fast rise/fall times, or slow rise/fall times from a heavily loaded bus due to parasitic capacitance build up.

Abiding by the electrical specifications in the standard helps to ensure that you will have accurate data and consistent I2C communication. If the user decides to exceed the specification limits, there might be issues in maintaining steady and accurate I2C communication especially when communicating at higher speeds.

I have seen customers in the past exceed bus capacitance limits going up to ~600pF on the I2C bus. It is possible, but you may have to introduce lower overall data rates as well as well as buffers/repeaters to deal with the high amount of parasitic capacitance.

Regards,

Tyler

Hi Tyler, Clemens

Thanks for your reply.

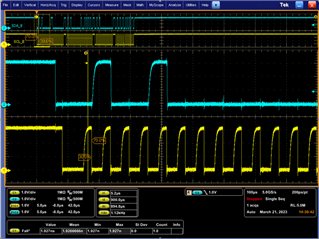

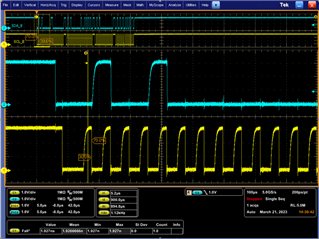

The I2C speed is around 400k, do you have any advice to slow down the falling edge? Change the pull up resistor and add the series resistance in the SCL and SDA doesn't work.

Does the falling edge matters in this speed? Thanks!

BR

Jiawei

If the falling edges are faster than the specification's limit, then this indicates that the drive strength is too high.

What device generates these falling edges? If it is a microcontroller, it should be possible to configure the drive strength. Otherwise, a series resistor and/or a small capacitor to GND would help.

Please note that an oscilloscope probe's ground clip can increase ringing.

Hi Jiawei,

I agree with Clemens' statement:

If the falling edges are faster than the specification's limit, then this indicates that the drive strength is too high.

Adjusting the drive strength via software, including a series resistor, and/or a small capacitor to GND are all viable solutions.

Regards,

Tyler