Other Parts Discussed in Thread: DP83TC814R-Q1, DP83TC814S-Q1

I just implement TDR follow below and snla389,but it often show 1:1 in 0x1E[1:0]

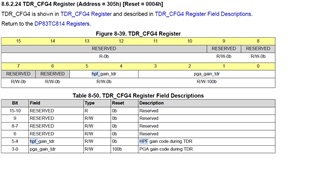

TDR is activated by setting bit[15] in register 0x1E. The procedure is as follows.

DP83TC814S-Q1, DP83TC814R-Q1

SNLS663 – DECEMBER 2021 www.ti.com

34 Submit Document Feedback Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: DP83TC814S-Q1 DP83TC814R-Q1

• Configure the DP83TC814-Q1 as per the initilization settings from SNLA389 Application Note

• Ensure that the Link Partner connected to the PHY is slient. Link will be down during TDR execution.

• Run the Pre-TDR configuration settings as listed in SNLA389.

• Start TDR by setting register 0x1E[15] to '1'.

• Wait 100ms, read register 0x1E[1:0]

– If it reads 0b10 then TDR has executed successfully.

• If TDR executed successfully then read register 0x310 to get TDR results.

– 0x310[8]: 0 = Half Wire Open not detected or 1 = Half Wire Open detected

– 0x310[7]: 0 = Cable fault not detected or 1 = Cable fault detected

– 0x310[6]: 0 = Cable fault is OPEN or 1 = Cable fault is SHORT

– If valid cable fault is detected then 0x310[5:0] will store the location value in meters.

my codes like below

eth_setRegister(0x0834, 0xC001,true);

sleep(1);

eth_setRegister(0x0523, 0x0001, false);

eth_setRegister(0x0827, 0x4800, false);

eth_setRegister(0x0301, 0x1701, false);

eth_setRegister(0x0303, 0x023d, false);

eth_setRegister(0x0305, 0x0015, false);

eth_getRegister(0x0306, regVal, false);

regVal = (regVal|0x0010);

eth_setRegister(0x0306, regVal, false);

eth_setRegister(0x001f, 0x4000, false);

usleep(120000);//wait for reset

eth_setRegister(0x0523, 0x0000, false);

eth_setRegister(0x001f, 0x0000, false);

ret = eth_setRegister(0x001e, 0x8000, false); //bit15 1: Start cable measurement 0:Cable Diagnostic is disabled

while(true)

{

ret = eth_getRegister(0x001E, regVal, false);

if(ret)

{

LOG(ERROR) << std::hex << regVal << endl;

measurementResult = regVal & 0x3; //bit 0:1

if(3 == measurementResult) //complete and fail

{

val = ETHERNET_OPEN_ERROR;

// LOG(ERROR) << "cable test failed" << endl;

return ret;

}

else if(2 == measurementResult) //complete and not fail

{

// LOG(WARNING) << "cable test completed success" << endl;

break;

}

else

{

//do nothing, loop

nRetryCnt++;

if(ETH_RETRY_READ_REG_MAX < nRetryCnt)

{

val = ETHERNET_UNKNOWN;

// LOG(ERROR) << "eth_getCableDiagResult, Retry failed !!!!!" << endl;

return ret;

}

usleep(ETH_DELAY_READ_REG_MS);

}

}

else

{

val = ETHERNET_OPEN_ERROR;

// LOG(ERROR) << "cable test failed,get register failed" << endl;

return ret;

}

}

ret = eth_getRegister(0x0310, regVal, false);

if(ret)

{

// LOG(ERROR) << std::hex << regVal << endl;

if(BIT_TST(regVal,7))

{

if(BIT_TST(regVal,6))

{

val = ETHERNET_OPEN_ERROR;

// LOG(ERROR) << "eth_getCableDiagResult ETHERNET_OPEN_ERROR1" << endl;

}

else

{

val = ETHERNET_SHORT_ERROR;

// LOG(ERROR) << "eth_getCableDiagResult ETHERNET_SHORT_ERROR" << endl;

}

}

else if(BIT_TST(regVal,8))

{

val = ETHERNET_OPEN_ERROR;

// LOG(ERROR) << "eth_getCableDiagResult ETHERNET_OPEN_ERROR2" << endl;

}

else

{

val = ETHERNET_NO_FAULT;

// LOG(ERROR) << "eth_getCableDiagResult ETHERNET_NO_FAULT" << endl;

}

}