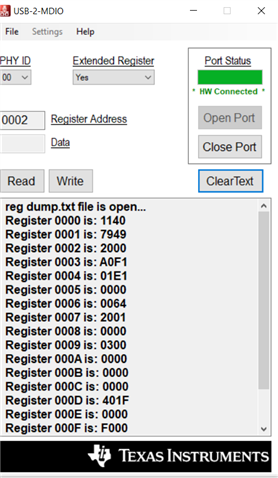

we are developing a board using DP83867 as the ethernet phy, we need help with its configuration as when I read the link status register, I always get 1 even without connecting the ethernet cable. So, is there any specific way of configuring it??

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.