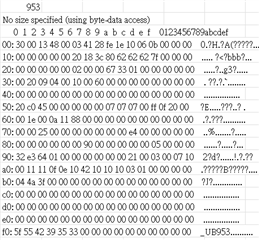

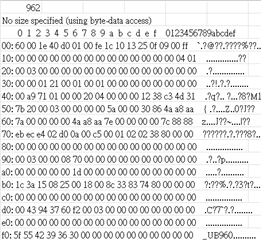

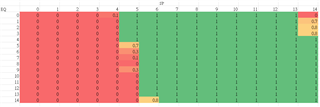

Hello, we are using UB962 (system) with 4 UB953 (cameras) in an asynchronous state, and we have found that the I2C signal output by UB953 is inconsistent with the signal output by the system to UB962 in specific camera modules. This issue occurs because there is a lot of data to be output through I2C, and the signal loss starts to happen in the middle or later stage of the output process. Please refer to the image below. There are no other devices on the UB953 I2C bus that could affect the signal. This problem occurs on some cameras but not on others. Interestingly, the abnormal cameras do not exhibit any abnormality in the I2C signal when they are set to synchronous mode. Could you advise us on which areas we should check?

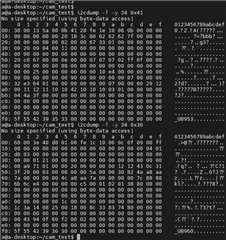

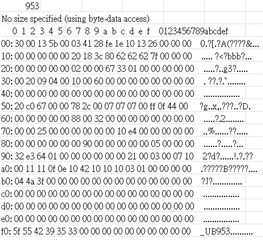

This is the signal in normal state.

This is the signal in abnormal state.